**Repositorio Digital USM**

https://repositorio.usm.cl

Tesis USM

TESIS de Pregrado de acceso ABIERTO

2020-12

# DISEÑO DE UNA PLACA DE CONTROL PARA EL MÓDULO DE UN TRANSFORMADOR DE ESTADO SÓLIDO

DATTWYLER RODRÍGUEZ, FERNANDO

https://hdl.handle.net/11673/49972

Repositorio Digital USM, UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

# DISEÑO DE UNA PLACA DE CONTROL PARA EL MÓDULO DE UN TRANSFORMADOR DE ESTADO SÓLIDO

### FERNANDO DATTWYLER RODRÍGUEZ

MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRÓNICO

PROFESOR GUÍA : DR. MARCELO PÉREZ L. PROFESOR CORREFERENTE : DR. CHRISTIAN ROJAS M.

$A\ mi\ familia\ \dots$

### **AGRADECIMIENTOS**

Este trabajo marca el fin de mi paso por la Universidad, en el cual muchas personas y momentos marcaron mi vida. Es por esto que en este pequeña nota espero expresar mis más sincera gratitud a cada uno de ellos.

Primeramente quisiera agradecer a mi familia, en especial a mis padres Fernando y Elena quienes me brindaron un apoyo incondicional incluso en los momentos más difíciles, no hay duda que sin ustedes no hubiese podido estar en donde me encuentro hoy. También fueron ustedes quienes me ayudaron a cumplir mi deseo de ir a Suecia a continuar mis estudios, en donde pude ver otra realidad que cambió mis sueños y metas.

A mis amigos del colegio Carlos, Eduardo y Joaquín, con los que formamos un lazo que perdura en el tiempo y siempre que vuelvo a La Serena nos reunimos para compartir nuestras vivencias. A Matías y Elías compañeros de múltiples laboratorios y ramos, estoy seguro que cada uno de esos momentos, incluyendo los malos ahora forman parte de buenas anécdotas. A mis compañeros del Powerlab, con los que siempre encontrábamos un buen momento para poder distendernos y pasar un buen rato. A Diego y Javier a quienes conocí más ya en la etapa final y que con las juntas que teníamos también me llevaron a ver las cosas de forma distinta. A Leonardo con quien compartimos en las Academias tecnológicas, Difusión, Powerlab y terminamos desarrollando nuestras Memorias de forma complementaria, además que su familia me acogió como si fuera uno más de ellos; hay mucho más pero quisiera reservármelo.

A los profesores de física René y Oscar quienes me dieron la confianza para ser su ayudante y que sin duda es parte importante de mi formación. Al profesor César que a pesar de su carácter, me dió una visión diferente sobre la pedagogía y también agradezco su preocupación para que el proceso de intercambio fuera exitoso.

Finalmente se encuentran los profesores Marcelo y Christian quienes me supervisaron durante esta Memoria y me ayudaron para que esta pudiera salir adelante a pesar de las dificultades presentes debido a la pandemia. Que este trabajo pudiera tener esta calidad, se las debo a su dedicación y tiempo a la hora de realizar sus correcciones y de darme consejos en su elaboración.

Fernando Dättwyler Rodríguez

### RESUMEN

La generación, transmisión y distribución de energía son las tres partes de un sistema eléctrico de potencia, en las cuales el transformador cumple un rol fundamental permitiendo transmitir la electricidad en grandes distancias con un alto nivel de eficiencia.

Recientemente, los avances de la electrónica de potencia y la implementación de redes inteligentes (Smart Grids), ha traído como consecuencia la popularización del uso de los transformadores de estado sólido (SST). La función de los SSTs es alcanzar el voltaje de la red usando un transformador de alta frecuencia con el fin de reducir el volumen y el peso de un transformador tradicional. Por otro lado, los SSTs permiten la regulación de voltaje y corriente, pudiendo así controlar el flujo de potencia bidireccionalmente y compensar fallas.

En este proyecto se diseñará una tarjeta para el control de un módulo SST, el cual considera la captura y procesamiento de datos provenientes desde el hardware de potencia, la comunicación con el sistema de control externo y la generación de disparos para los semiconductores. Asimismo, es diseñado el sistema lógico que permite unir los elementos mencionados. El diseño PCB de la tarjeta es realizada en ALTIUM DESIGNER y el sistema lógico es implementado en la FPGA LATTICE MACHXO2-HC2000. En este documento se encuentran los esquemáticos y lista de componentes necesarios para el montaje de la tarjeta, además de los códigos del sistema lógico implementado.

Palabras Clave. Transformador de estado sólido, Diseño PCB, Dispositivos lógicos programables, VHDL.

### ABSTRACT

Generation, transmission and distribution are the three main parts of an electrical power system, in which the transformer has a fundamental role, allowing transmission over long distances with high efficiency.

Recently, due to the development of power electronics and the implementation of Smart Grids, the use of solid-state transformers (SST) has been popularized. The function of the SSTs is to reach the grid voltage using a high-frequency transformer in order to reduce the volume and weight of a traditional transformer. Moreover, SSTs allow the current and voltage regulation, making bidirectional power flow and fault compensation possible.

In this project, a control board for a SST module is designed, which considers the capture and processing of data coming from the converter, the communication with the external control system and generation of the switching pulses. Likewise, the logical system that links the mentioned elements is designed. The PCB layout is designed in ALTIUM DESIGNER and the logic system is implemented in the FPGA LATTICE MACHXO2-HC2000. This document contains the schematics and bill of materials necessary for the assembly, besides the codes for the logic system implemented.

Keywords. Solid-State Transformer, PCB desing, Programmable logic devices, VHDL.

## Índice de Contenidos

| 1. | Intr | roducción                                                 | 1               |

|----|------|-----------------------------------------------------------|-----------------|

|    | 1.1. | Contribuciones                                            | 1               |

|    | 1.2. | Objetivo General, Específicos, Alcances y Limitaciones    | 1               |

|    |      | 1.2.1. Objetivos específicos                              | 1               |

|    |      | 1.2.2. Alcances                                           | 2               |

|    |      | 1.2.3. Limitaciones                                       | 2               |

| 2. | Esta | ado del Arte                                              | 3               |

|    | 2.1. | Transformadores de estado sólido                          | 3               |

|    | 2.2. | Dispositivos lógicos programables                         | 7               |

|    |      | 2.2.1. Microcontroladores                                 | 7               |

|    |      | 2.2.2. Procesadores digitales de señales                  | 12              |

|    |      |                                                           | 16              |

|    | 2.3. | Comunicación Serie                                        | 21              |

|    |      | 2.3.1. SPI (Serial Peripheral Interface)                  | 21              |

|    |      | 2.3.2. I2C                                                | 22              |

|    |      | 2.3.3. Universal Asynchronous Receiver Transmitter (UART) | 23              |

|    |      | 2.3.4. Universal Synchronous/Asynchronous                 |                 |

|    |      | Receiver Transmitter (USART)                              | 23              |

| 3. | Dise | eño de Tarjeta de Pruebas                                 | 25              |

| •  | 3.1. |                                                           | 25              |

|    | 3.2. | Elección de Integrados                                    | 25              |

|    |      |                                                           | 26              |

|    |      |                                                           | 28              |

|    |      | 9                                                         | 28              |

|    |      |                                                           | 32              |

|    |      | •                                                         | 35              |

|    |      |                                                           | 36              |

|    | ъ.   | ~                                                         |                 |

| 4. |      | eño Lógico y<br>ales de la Tarjeta de Control             | 38              |

|    |      |                                                           | 38              |

|    |      | •                                                         | 40              |

|    |      | <del>-</del>                                              | 40<br>40        |

|    |      |                                                           | 44              |

|    | 4.4. | •                                                         | $\frac{14}{45}$ |

|    |      |                                                           | 46              |

|    |      |                                                           | $\frac{40}{49}$ |

|    |      |                                                           | 49<br>53        |

|    |      |                                                           | ეკ<br>53        |

|    |      | •                                                         |                 |

|    |      | 4.4.6. Interfaz ADC                                       | 55              |

|    | 4.5.  | Elección de componentes                   | 56               |

|----|-------|-------------------------------------------|------------------|

|    | 4.6.  | Aritmética y simbolización de las señales | 56               |

|    |       | 4.6.1. Conversión de mediciones           | 56               |

| 5  | Dise  | eño electrónico de la                     |                  |

| •  |       |                                           | 58               |

|    |       |                                           | 58               |

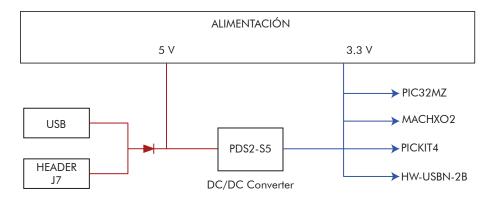

|    | 5.2.  | Diagrama de alimentación                  | 58               |

|    |       | · ·                                       | 59               |

|    | 5.4.  | Esquemáticos                              | 32               |

|    | 5.5.  | Lista de Materiales                       | 66               |

|    | 5.6.  | Dimensiones y Vistas                      | 37               |

| 6  | Res   | ultados                                   | 39               |

| ٠. |       |                                           | 39               |

|    |       | · · · · · · · · · · · · · · · · · · ·     | 70               |

|    |       |                                           | 72               |

|    |       | T                                         | . <b>–</b><br>74 |

|    |       |                                           | 75               |

|    |       |                                           | 77               |

|    | 6.7.  |                                           | 78               |

|    | 6.8.  | -                                         | 79               |

|    | 6.9.  | Costos de Producción                      | 79               |

| 7. | Con   | aclusiones                                | 80               |

|    |       |                                           |                  |

| Bi | bliog | grafía 8                                  | <b>32</b>        |

| Α. | AN    | EXO 1                                     | <b>34</b>        |

| В. | AN    | EXO 2                                     | 36               |

|    | B.1.  | Main                                      | 36               |

|    | B.2.  | TX UART                                   | 92               |

|    | B.3.  | RX UART                                   | 96               |

|    |       |                                           | 98               |

|    |       | Módulo de Disparos                        |                  |

|    |       | Unidad de Control Central                 |                  |

|    | B.7.  | Interfaz ADC                              | )6               |

|    | B.8.  | Declaración de Entradas/Salidas           | )9               |

ÍNDICE DE TABLAS ÍNDICE DE TABLAS

## Índice de Tablas

| 2.1. | Familias de microcontroladores Texas Instruments | 10 |

|------|--------------------------------------------------|----|

| 2.2. | Familias de microcontroladores Microchip         | 11 |

| 2.3. | Familias de microcontroladores NXP               | 12 |

| 2.4. | Familias de DSPs                                 | 16 |

| 2.5. | Familias FPGA XIllinx e Intel                    | 19 |

| 2.6. | Familias de FPGAs Lattice                        | 20 |

| 2.7. | Comparación de dispositivos lógicos programables | 20 |

| 2.8. | Comparación de buses de comunicación serial      | 24 |

| 3.1. | Pinout Header J1                                 | 29 |

| 3.2. | Pinout Header J4                                 | 29 |

| 3.3. | Pinout Header J2                                 | 29 |

| 3.4. | Pinout Header J3                                 | 30 |

|      | Pinout Header J5                                 |    |

|      | Pinout Header J6                                 |    |

| 3.7. | Lista de materiales Tarjeta de Pruebas           | 35 |

| 5.1. | Pinout Header J1                                 | 60 |

| 5.2. | Pinout Header J2                                 | 61 |

| 5.3. | Lista de materiales Tarjeta de Control           | 66 |

| 6.1. | Mediciones de pruebas módulo UART                | 71 |

| 6.2. | Mediciones de disparos a los puentes SM1 / SM2   | 73 |

| 6.3. | Mediciones de disparos a los puentes SP / SS     | 73 |

| 6.4. | Tiempos de las tareas de Inicialización          | 78 |

| 6.5. | Tiempos asociados a la ruta crítica del sistema  | 78 |

| 6.6. | Recursos utilizados por la FPGA                  | 79 |

| 6.7. | Costos de producción                             | 79 |

ÍNDICE DE FIGURAS ÍNDICE DE FIGURAS

# Índice de Figuras

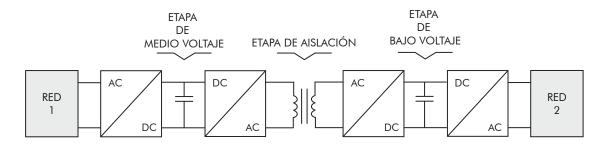

| 2.1.  | Diagrama de etapas SST                                                               | 4  |

|-------|--------------------------------------------------------------------------------------|----|

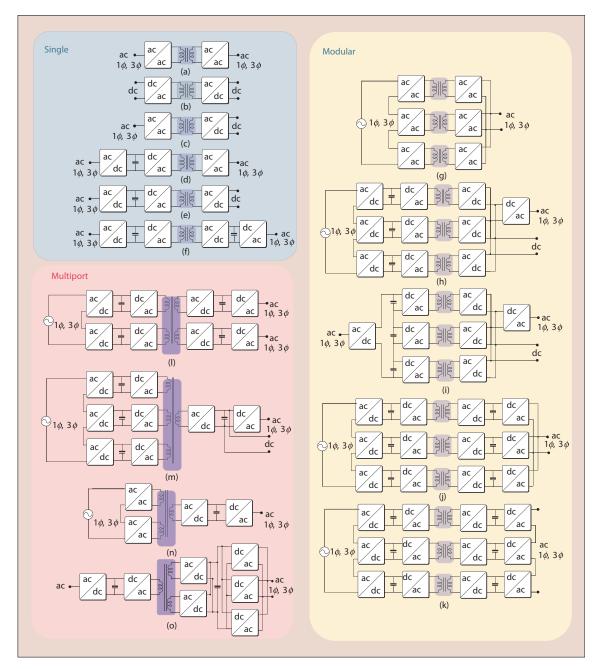

| 2.2.  |                                                                                      | 5  |

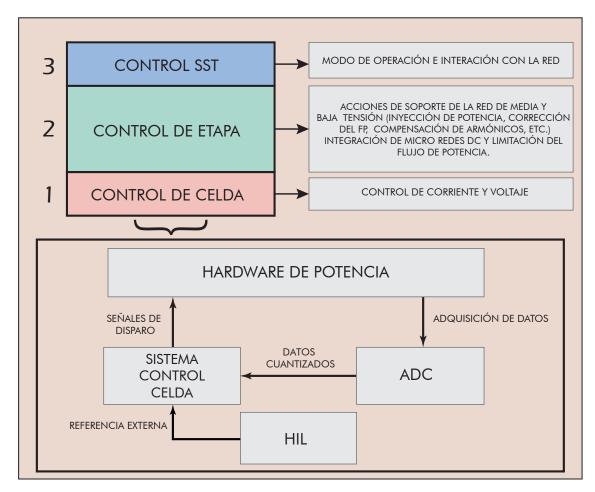

| 2.3.  | Diagrama y estructura de control para el SST                                         | 6  |

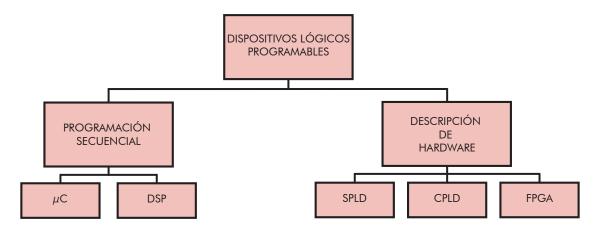

|       |                                                                                      | 7  |

| 2.5.  |                                                                                      | 8  |

| 2.6.  | Esquema de familias de microcontroladores                                            | 9  |

|       | Diagrama simplificado de la arquitectura de un DSP                                   | 3  |

| 2.8.  | Esquema familias DSPs                                                                | 5  |

| 2.9.  | Arquitectura de una FPGA                                                             | 7  |

|       | Esquema familias FPGAs                                                               | 8  |

|       | Diagrama de comunicación SPI                                                         |    |

|       | Bus de transmisión SPI                                                               |    |

|       | Diagrama de comunicación I2C                                                         |    |

| 2.14. | Bus de transmisión I2C                                                               |    |

| 2.15. | Trama de bits para comunicación UART (cambiar)                                       |    |

|       | Diagrama de comunicación UART                                                        |    |

| 2.17. | Diagrama de comunicación USART                                                       | 4  |

| 0.1   |                                                                                      | _  |

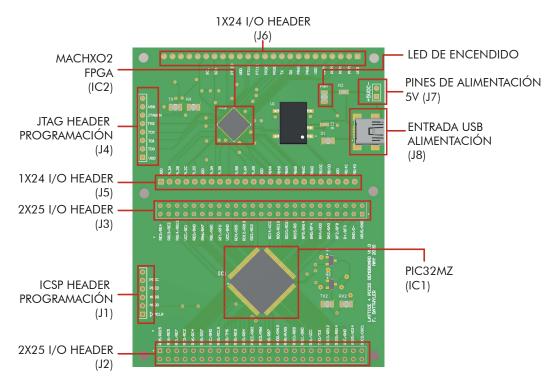

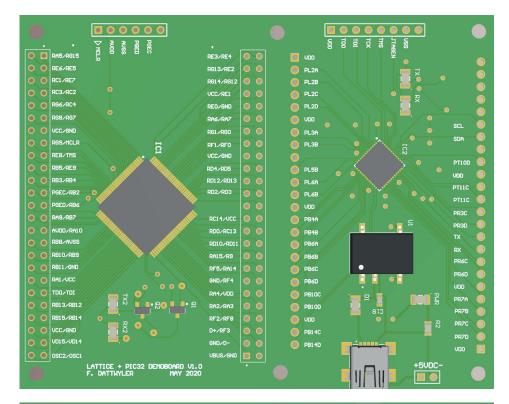

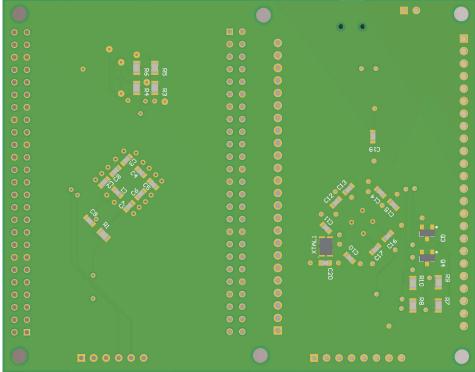

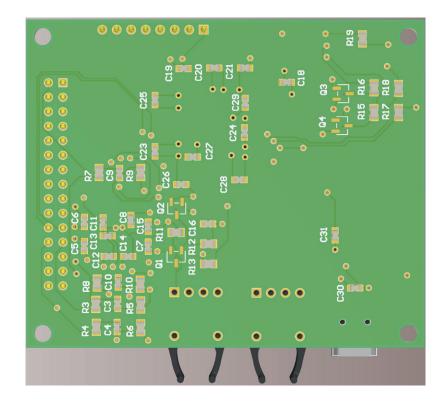

|       | Vista superior de la tarjeta de Pruebas                                              |    |

|       | Diagrama de alimentación de la Tarjeta de Pruebas                                    |    |

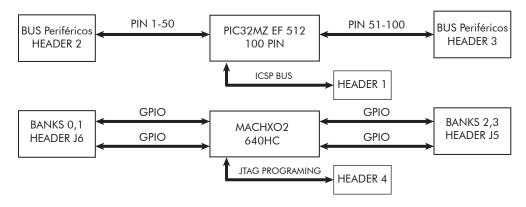

|       | Diagrama de distribución de pines de la Tarjeta de Pruebas                           |    |

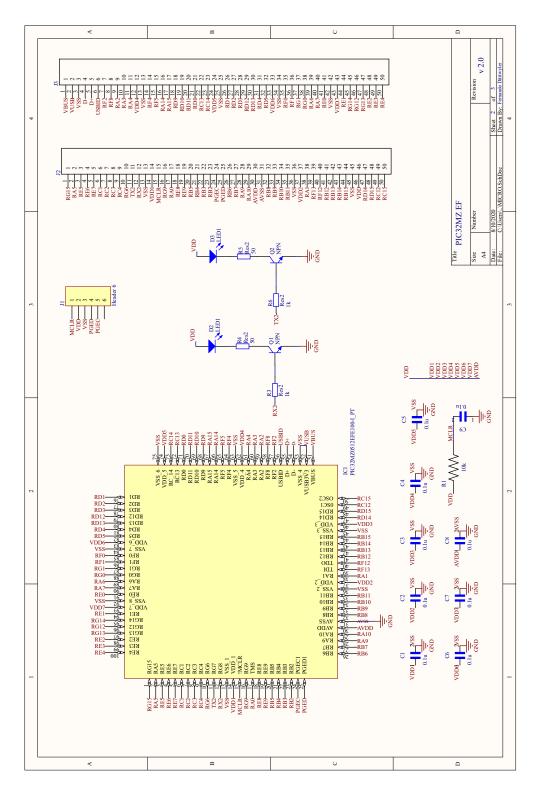

|       | Esquemático del microcontrolador PIC32                                               |    |

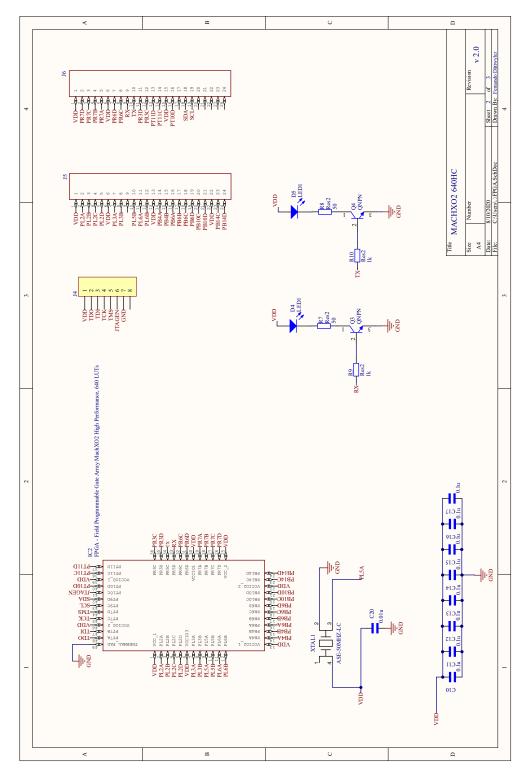

|       | Esquemático de la FPGA MACHX02                                                       |    |

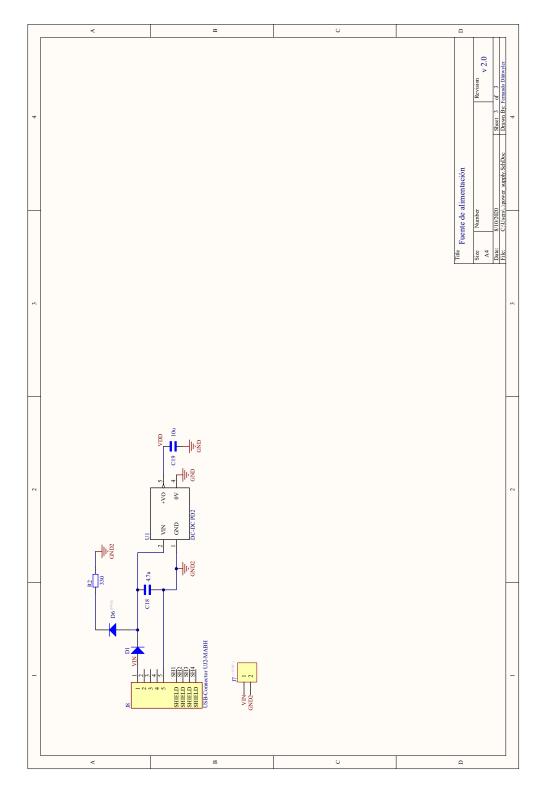

|       | Esquemático de la fuente de alimentación                                             |    |

|       | Vistas superior e inferior de la tarjeta de Pruebas                                  |    |

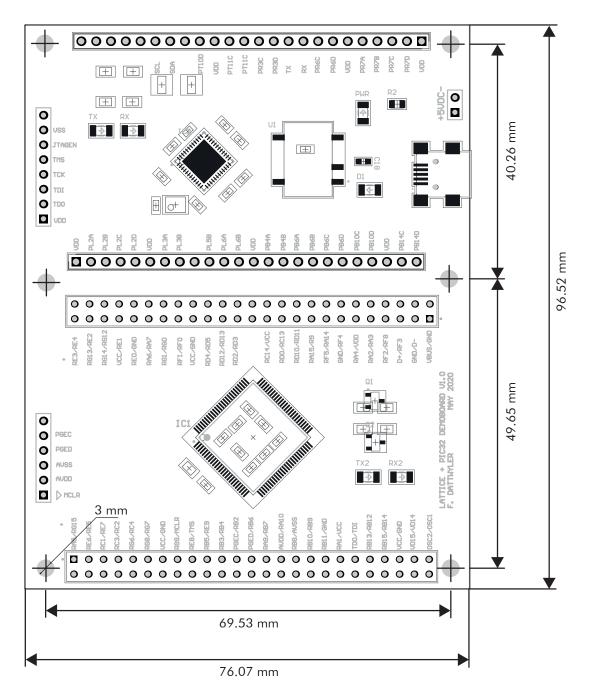

| 3.8.  | Dimensiones físicas de la tarjeta de Pruebas                                         | 1  |

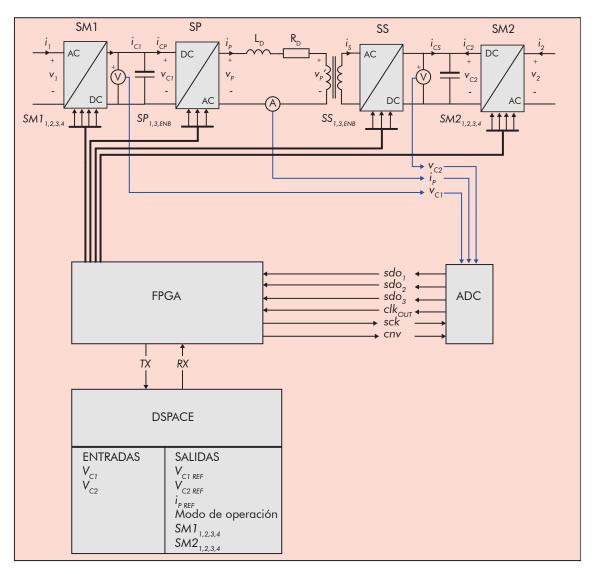

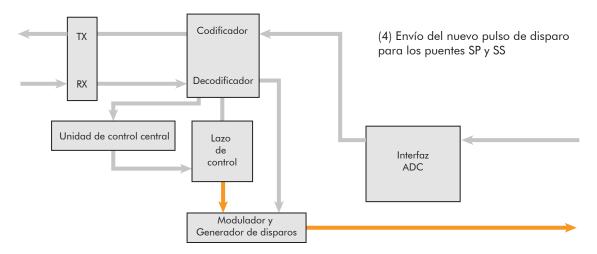

| 4.1.  | Diagrama del Sistema de estudio                                                      | 9  |

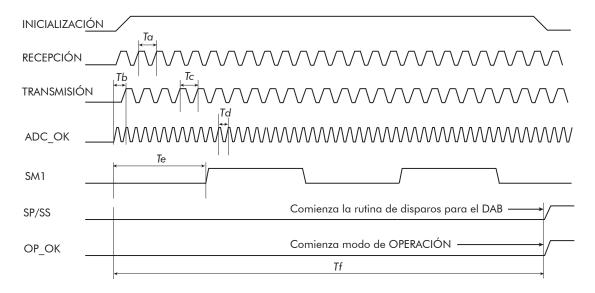

|       | Diagrama de tiempo para la operación de Inicialización                               |    |

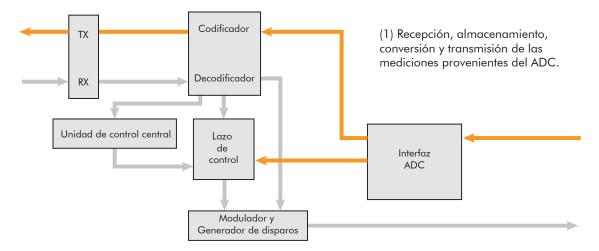

|       | Adquisición y transmisión de mediciones hacia el Sistema de Control Externo 4        |    |

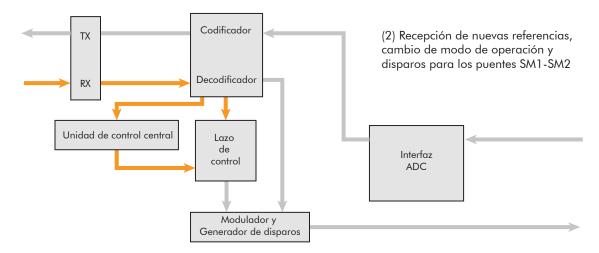

|       | Recepción y decodificación de mensajes provenientes del Sistema de Control Externo 4 |    |

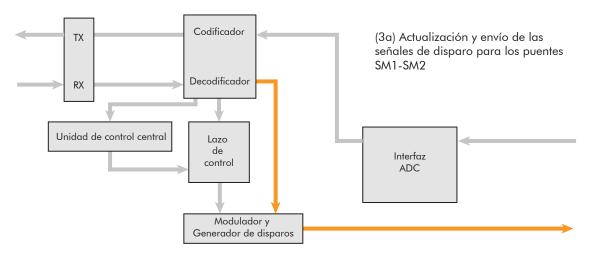

|       | Envío de pulsos a los puentes SM1 y SM2                                              |    |

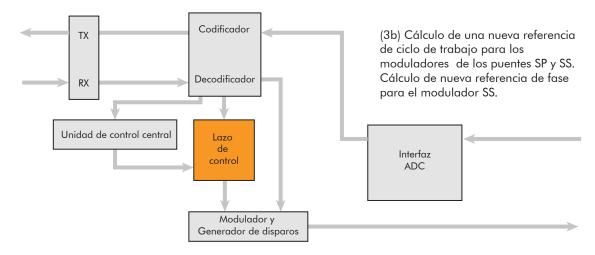

|       | Cálculo de nuevas salidas del Lazo de Control                                        | 2  |

| 4.7.  | Envío de pulsos a los puentes SP y SS                                                | .3 |

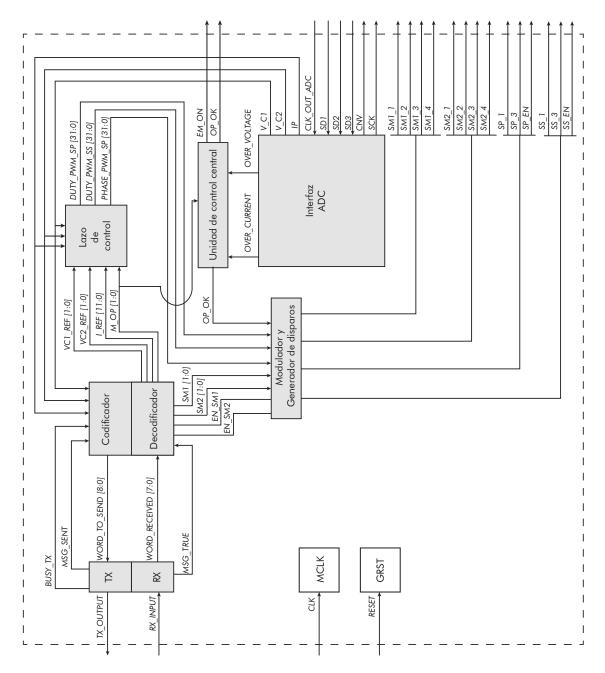

| 4.8.  | Diagrama de bloques del sistema lógico                                               | 4  |

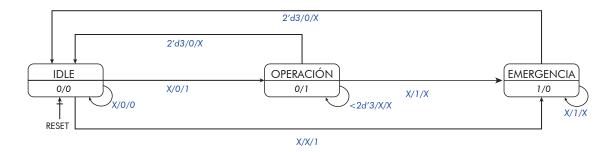

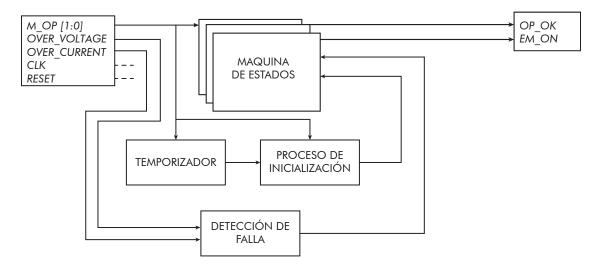

|       | Maquina de estados Unidad de Control Central                                         | .5 |

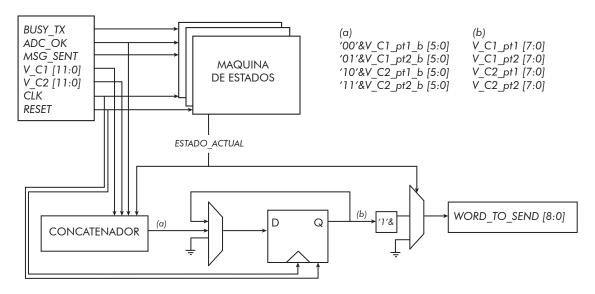

|       | Diagrama de la Unidad de Control Central                                             | 6  |

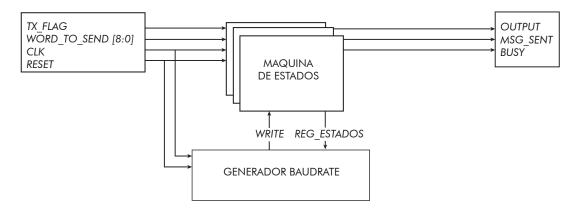

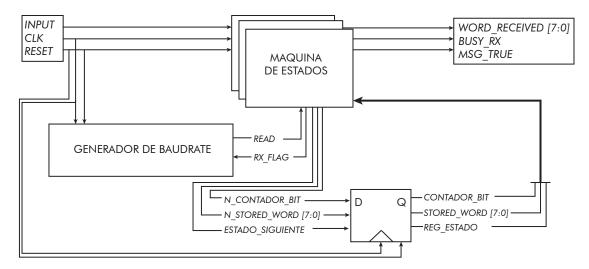

|       | Diagrama del transmisor                                                              | 7  |

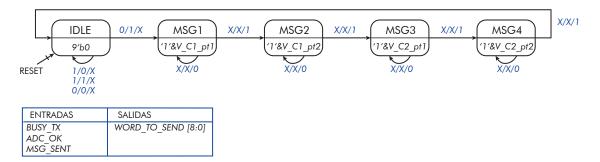

|       | Máquina de estados para el módulo de transmisión                                     | 7  |

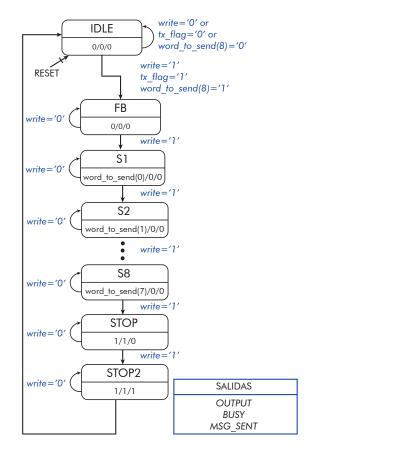

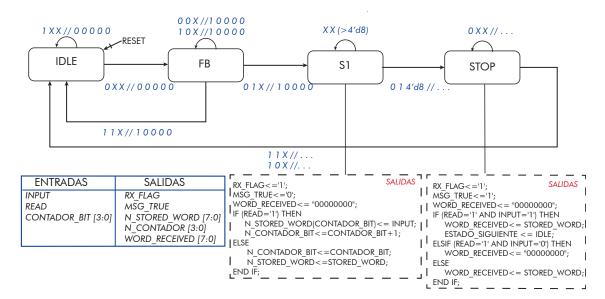

|       | Diagrama del receptor                                                                | 8  |

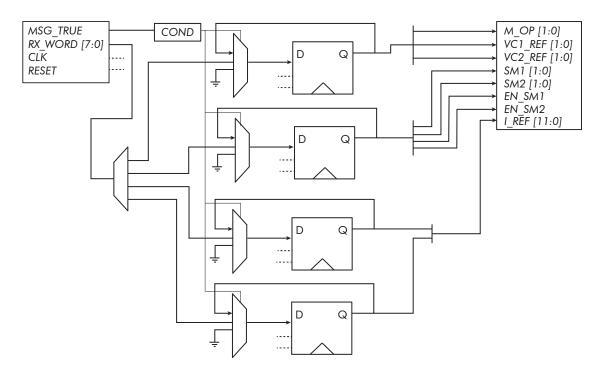

|       | Máquina de estados para el módulo de recepción                                       | .9 |

| 4.15. | Máquina de estados para el módulo de codificación                                    | 0  |

ÍNDICE DE FIGURAS ÍNDICE DE FIGURAS

| 4.16. | Máquina de estados para el módulo de codificación                                             | 50 |

|-------|-----------------------------------------------------------------------------------------------|----|

| 4.17. | Lista de Codificación de Mensajes                                                             | 52 |

| 4.18. | Diagrama del decodificador                                                                    | 52 |

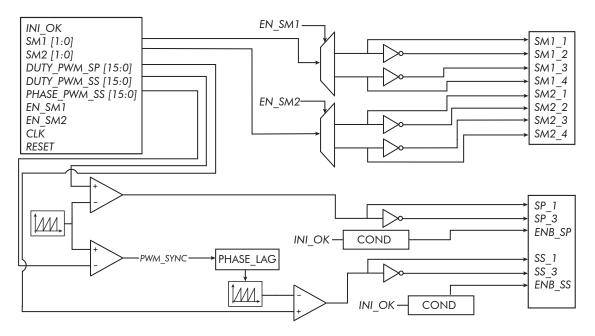

|       | Diagrama del Disparador                                                                       |    |

| 4.20. | Diagrama Interfaz ADC                                                                         | 55 |

| 5.1.  | Diagrama de alimentación Placa de Control                                                     | 59 |

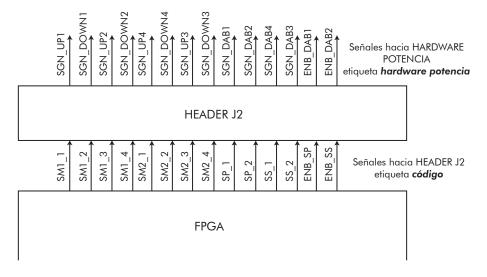

| 5.2.  | Diagrama de buses Placa de Control                                                            | 59 |

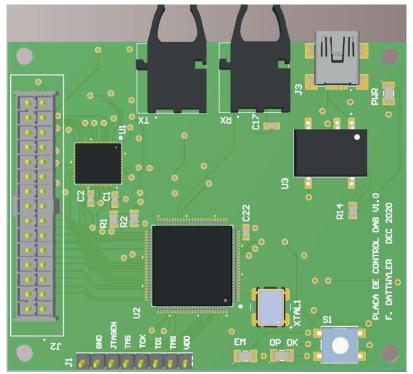

| 5.3.  | Vista de superficial Tarjeta de control                                                       | 60 |

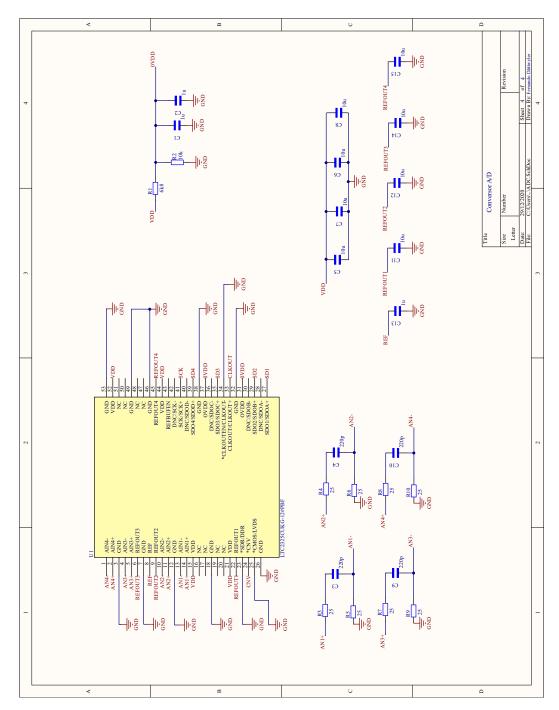

| 5.4.  | Esquemático del conversor análogo digital                                                     | 62 |

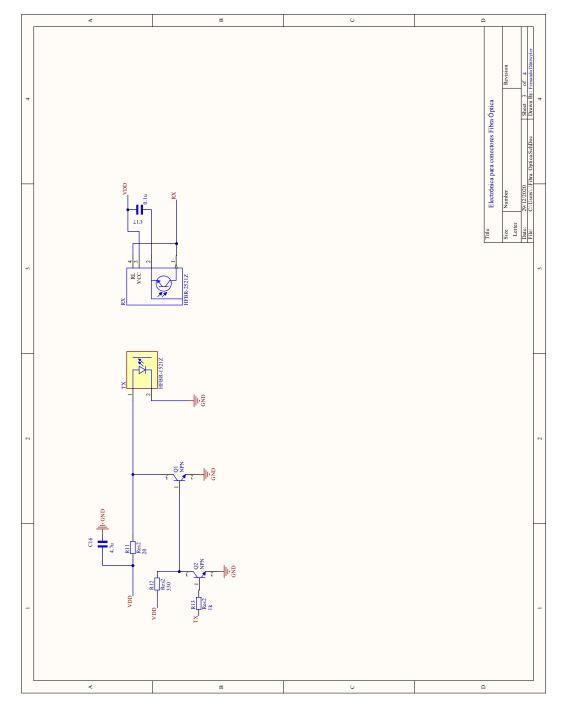

| 5.5.  | Esquemático de los conectores de fibra óptica                                                 | 63 |

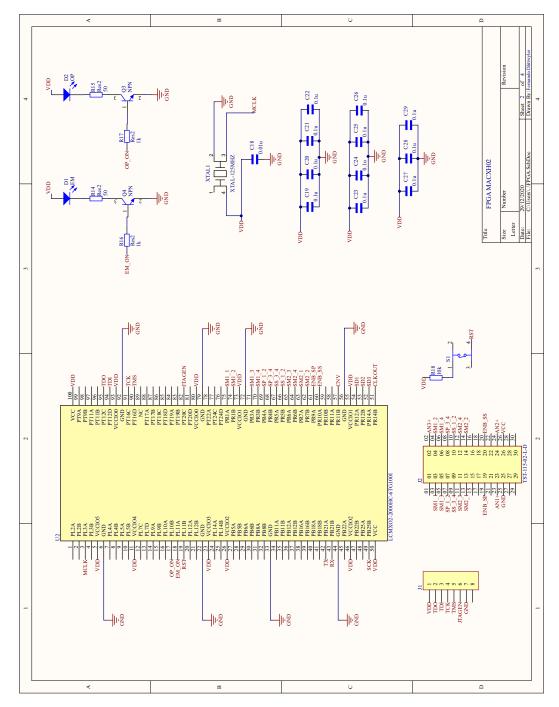

| 5.6.  | Esquemático de la FPGA MACHXO2-2000                                                           | 64 |

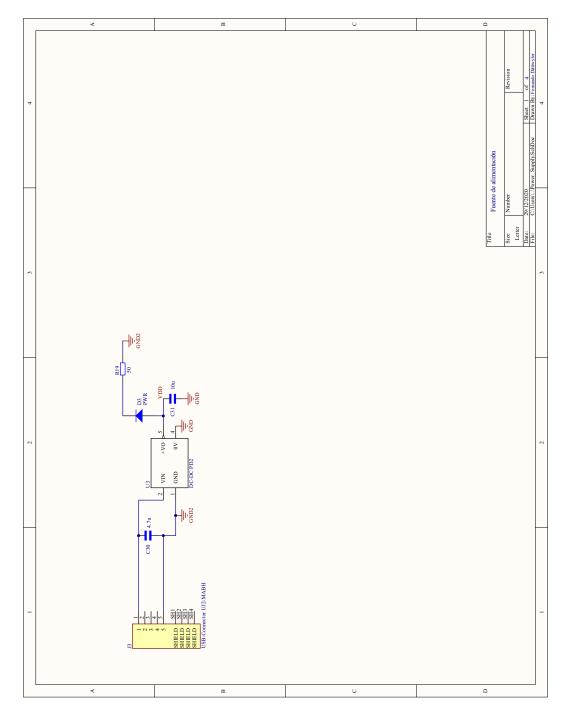

| 5.7.  | Esquemático de la fuente de alimentación $\dots \dots \dots \dots \dots \dots$                | 65 |

| 5.8.  | Vistas superior e inferior de la Tarjeta de Control                                           | 67 |

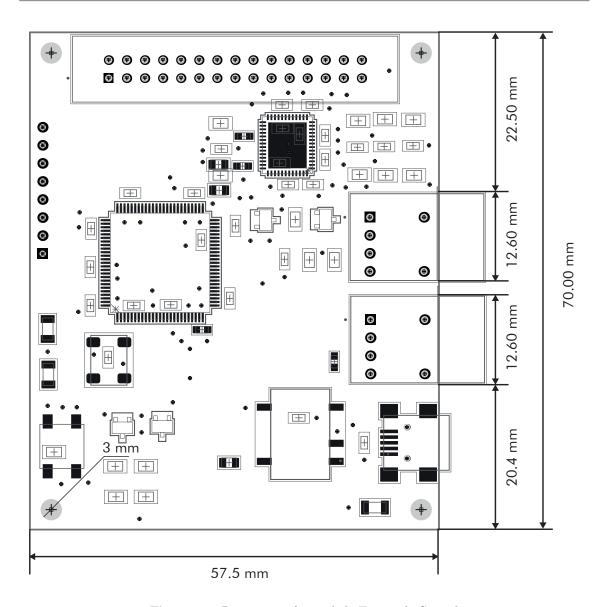

| 5.9.  | Dimensiones físicas de la Tarjeta de Control                                                  | 68 |

| 6.1.  | Placa de evaluación y analizador lógico                                                       | 69 |

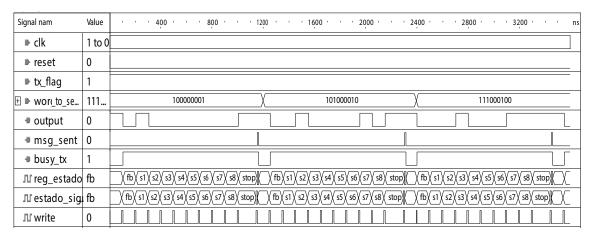

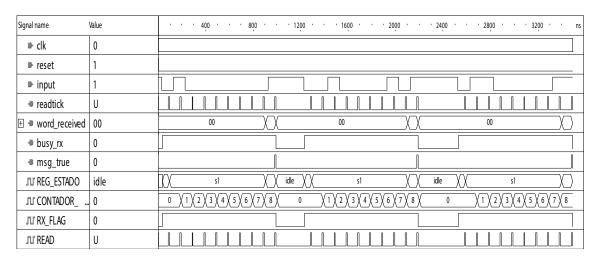

| 6.2.  | Simulación Modulo UART TX                                                                     | 70 |

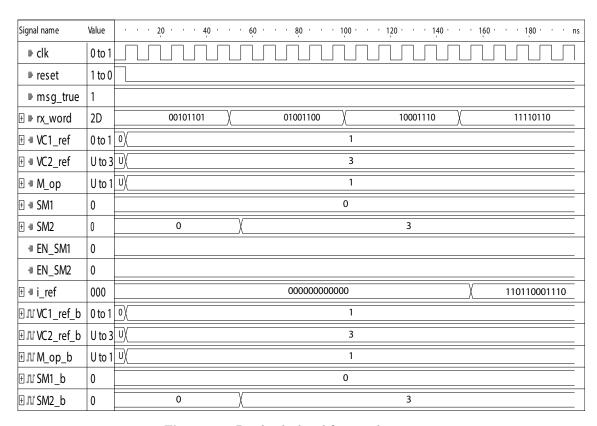

| 6.3.  | Simulación Modulo UART RX                                                                     | 70 |

| 6.4.  | Medición del módulo UART                                                                      | 71 |

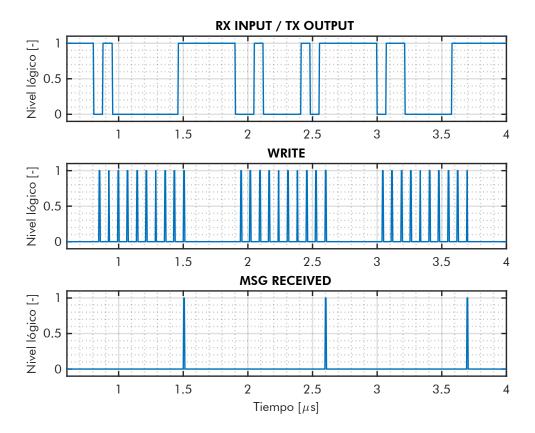

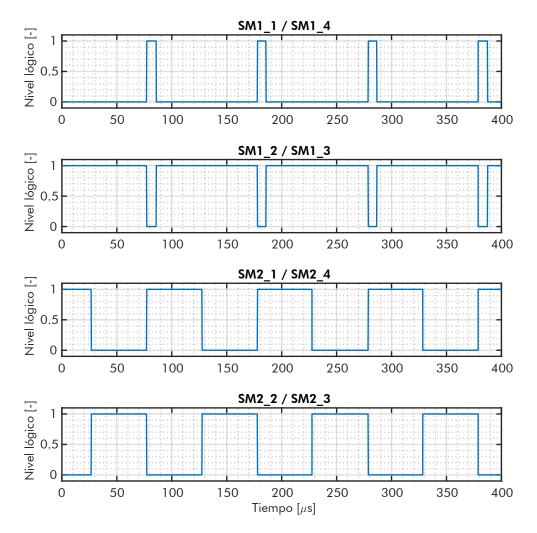

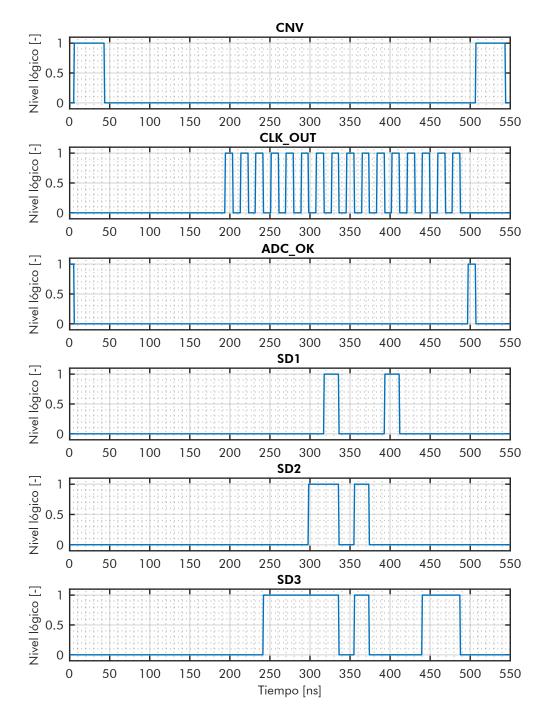

| 6.5.  | Secuencia de pulsos de disparo para los puentes SM1 y SM2                                     | 72 |

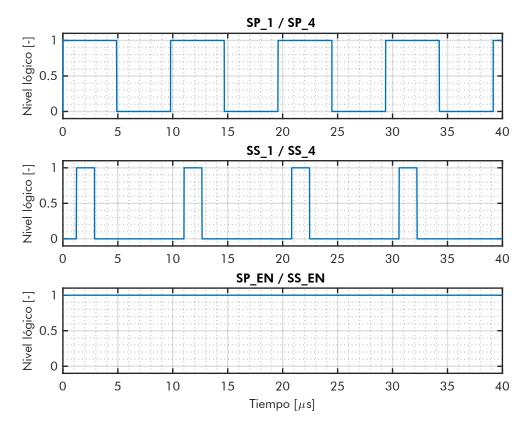

| 6.6.  | Secuencia de pulsos de disparo para los puentes SP y SS                                       | 73 |

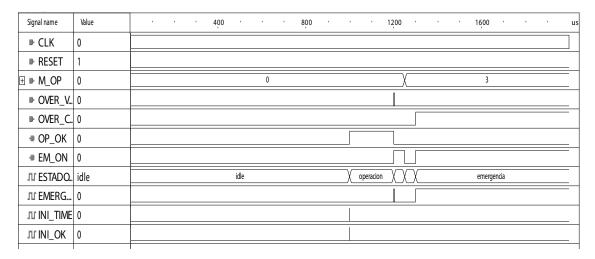

| 6.7.  | Prueba Módulo de control Central                                                              | 74 |

| 6.8.  | Prueba de codificación de mensajes                                                            | 76 |

| 6.9.  | Prueba de decodificación de mensajes                                                          | 76 |

| 6.10. | Máquina de estados para el módulo de recepción $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 77 |

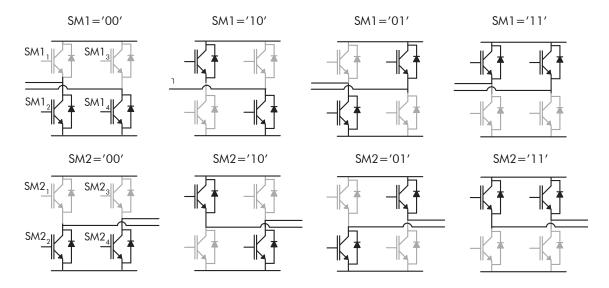

| A.1.  | Etiqueta de señales de semiconductores                                                        | 84 |

| A.2.  | Semiconductores encendidos por señal de control SM1 y SM2 $\dots \dots \dots$                 | 85 |

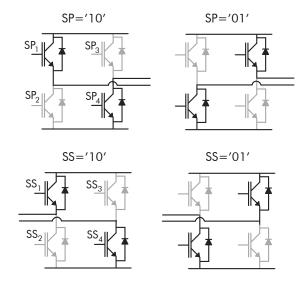

| A.3.  | Semiconductores encendidos por señal de control SP y SS                                       | 85 |

### 1 Introducción

L'a Memoria de Titulación "Diseño de una tarjeta de Control para el módulo de un Transformador de Estado Sólido", busca realizar mediante el uso de software, el diseño de una tarjeta electrónica que permita controlar el flujo de potencia de un transformador de estado sólido (SST).

Esta tarjeta de control recibe las mediciones de voltaje, corriente y temperatura para el procesamiento y posterior cálculo de los pulsos de disparo que actúan sobre los semiconductores. El diseño además incluye una conexión por fibra óptica para la adición de un elemento de control externo del tipo 'Hardware in the loop' (HIL) que permita simular situaciones o entregar referencias al sistema.

El proyecto comienza con una revisión de las topologías de los transformadores de estado sólido y sus aplicaciones, con esto se obtendrán los requisitos necesarios para su control. A partir de esto, se realizará un estudio de las principales familias lógicas programables como lo son microcontroladores, FPGAs y DSPs. Con la comparación de las familias existentes en el mercado, se evaluará él o los dispositivos que satisfacen los requerimientos de control y comunicación. Respecto a este último punto se hará un resumen de los principales protocolos de comunicación serial con sus usos y comparaciones.

Tomando en consideración la información recopilada acerca de los requerimientos de la tarjeta, presupuesto y desempeño del circuito, se pasará a la etapa de compra de componentes. En paralelo, se realizará el diseño en software y la programación de los integrados en simuladores.

El proyecto culmina con la finalización del diseño de la tarjeta, que incluye el sistema digital y el hardware que permite la posterior implementación del control.

### 1.1. Contribuciones

La solución aplicada en el diseño del hardware de control para este convertidor modular, permitirá a este regular el voltaje, corriente y dirección del flujo de potencia, las cuales son funciones necesarias para su operación. Además se encuentra el aprendizaje involucrado en el diseño en software de tarjetas electrónicas y el sistema digital que permite comunicar, integrar y realizar las acciones antes mencionadas.

### 1.2. Objetivo General, Específicos, Alcances y Limitaciones

El objetivo de la memoria es diseñar una tarjeta para el control de un módulo SST y la programación asociada a la captura y procesamiento de los datos de medición, configuración de la línea de comunicación y cálculo de los disparos para el hardware de potencia.

### 1.2.1. Objetivos específicos

Los objetivos específicos se establecen por cada capítulo y son listado a continuación:

- Recopilar información de topologías y estructura del control del transformador de estado sólido.

- Diseñar tarjeta de pruebas y simular de los integrados de la tarjeta.

- Definir módulos, sub-módulos y flujo de señales de la tarjeta de control.

- Realizar pruebas preliminares de comunicación y adquisición de datos para los integrados de la Tarjeta de pruebas.

- Elección de componentes, realización de esquemáticos y diseño en PCB de la tarjeta de control.

- Medir y obtener resultados del diseño implementado.

#### 1.2.2. Alcances

Esta Memoria sólo contempla el diseño y construcción de la tarjeta de control. El hardware de potencia para la cual se dedica, ya se encuentra diseñada por otro equipo del proyecto.

#### 1.2.3. Limitaciones

Las tareas a desarrollar en esta memoria se encuentran insertas en un proyecto FONDECYT (N°1181839), el cual financia y tiene por objetivo estimular el desarrollo de investigación científica y tecnológica del país. El profesor a cargo tiene la tarea de determinar y organizar los fondos adjudicados para este.

La Memoria contempla una duración de un año en donde se deben cumplir todos los objetivos listados anteriormente. Esta se desarrolla durante los años 2019-2020 los cuales se han visto marcados por la pandemia del COVID-19, la cual ha provocado medidas de confinamiento, entre las cuales se encuentra el cierre de la Universidad y sus laboratorios. Por lo que tareas experimentales y el montaje de la tarjeta se han visto acotadas y reemplazadas por otras de simulación. Esto para poder cumplir los plazos y condiciones de la Titulación.

### 2 Estado del Arte

En este capítulo se recopilará la información necesaria para sentar la bases técnicas que involucran el tema de esta Memoria. Este se encuentra dividido en tres secciones, la primera trata sobre los Transformadores de estado sólido en donde se exponen sus topologías y necesidades de control. La segunda parte trata sobre los dispositivos lógicos programables que son comúnmente utilizados para este tipo de aplicaciones y sus comparaciones. Finalmente se revisan los buses de comunicación serial, para los cuales se exponen sus principales características.

### 2.1. Transformadores de estado sólido

El desarrollo que han tenido los semiconductores de potencia en las últimas décadas han incrementado la presencia de estos en aplicaciones de alta potencia, industriales y transmisión de energía. A pesar de esto, la tecnología es reciente y nuevas contribuciones por parte de la academia y la industria han sido generadas en la actualidad [1]. El objetivo de esta sección es hacer una revisión de las topologías y estructuras de este tipo de convertidores.

Los transformadores convencionales han sido una pieza clave en los sistemas de transmisión de corriente alterna por su robustez, confiabilidad y capacidad de operar a distintos niveles de voltajes y potencia, además de ser resilientes a fallas. A pesar de esto, nuevas funcionalidades requeridas por la integración de sistemas de energía distribuidos (basados en energía renovable), electromovilidad y sistemas de tracción, suponen desafíos para elementos tradicionales en la conversión de energía [2]. Es por esto que desventajas como el volumen, tamaño, comportamiento pasivo ante armónicos, falta de regulación de voltaje y factor de potencia hacen necesaria una alternativa a los transformadores convencionales. Los SSTs en su estado actual son menos eficientes operando en condiciones nominales y resultan más complejos en su operación. Estos por su parte permiten el flujo bidireccional de potencia, conexión y desconexión de cargas y fuentes de alimentación, además de el control en la calidad de energía [3].

Los convertidores puente-H en cascada fueron el primer convertidor multinivel que fue teorizado a finales de la década de 1960'. La patente del convertidor de cuatro cuadrantes a base de tiristores de W. McMurray [4] que utiliza este tipo de topología, representa el antepasado directo de los SST modernos. Este tipo de convertidores no tuvieron una aplicación industrial hasta llegada la década de 1990', cuando los semiconductores permitieron trabajar a alto voltaje y frecuencia, haciendo posible que la densidad de potencia aumentara y fuera viable la aplicación de estos [5].

Con el pasar de los años los convertidores multinivel se han impuesto como la solución preferida en media tensión [1]. La configuración en serie y salida en paralelo ha servido como base para los primeros convertidores modulares SST de media a baja tensión, dada la capacidad de operación de alto voltaje en la entrada y de corriente en la salida [6]. Empresas como ABB [7], Alstom [8] y Siemens [9, 10, 11, 12] han presentado prototipos para este tipo de modelos.

La literatura ha propuesto diferentes tipos de arquitecturas las cuales tienen una composición de etapas que pueden descritas como [6, 8]:

- Etapa de entrada de media tensión: Esta etapa corresponde a un convertidor AC-AC ó AC/DC, el cual interactúa con la red de media tensión de la red general. El convertidor puede participar en la regulación del factor de potencia absorbiendo o inyectando potencia reactiva, reduciendo así las pérdidas de la red asociada al flujo de potencia reactiva y reduciendo las caídas o elevaciones de la tensión.

- Etapa de aislación: El convertidor DC/DC de esta etapa reduce el voltaje de entrada y provee aislación galvánica por medio de un transformador de alta frecuencia. Esta aislación evita que la distorsión harmónica y perturbaciones del voltaje provenientes de la red pase al lado de baja tensión y viceversa, por lo que permite la integración de sistemas de generación distribuidos o estaciones de carga de vehículos eléctricos.

- Etapa de bajo voltaje: Este convertidor que puede ser AC/AC ó DC/AC, interactúa con el lado de bajo voltaje de la red que normalmente corresponden a las cargas (de una o más fases). El convertidor compensa el desbalance, caídas y contenido armónico que generan las cargas. En esta etapa pueden ser agregadas funciones de mediciones para el monitoreo del consumo, identificación de la carga y control de la generación o consumo del lado de bajo voltaje.

Figura 2.1: Diagrama de etapas SST

Las arquitecturas que han sido desarrolladas pueden ser clasificadas por por su topología, estas son mencionadas a continuación [6, 8]:

- Arquitectura de aislación simple: Esta clasificación incluye a todos los SSTs que contienen sólo un transformador monofásico de alta frecuencia, que conecta la etapa de media y baja tensión.

- Arquitectura de aislación modular: Esta arquitectura se caracteriza por tener múltiples convertidores DC/DC conectados a través de un transformador monofásico. Esta arquitectura mejora la eficiencia pudiendo apagar celdas de los convertidores en paralelo cuando la carga disminuye. También aumenta la confiabilidad repartiendo la potencia que entrega cada celda. Estos modelos proveen la escalabilidad del voltaje y corriente permitiendo tener flexibilidad en el diseño y mantención.

- Arquitectura de aislación multipuerto: Esta clasificación incluye a todos las topologías que incluyen transformadores de devanados múltiples en la etapa de aislación. Dado el acoplamiento magnético, el SST puede intercambiar energía entre los puertos, haciendo un balance de la energía entregada en la carga. Esta capacidad permite redirigir la potencia en caso de fallas y por lo tanto se aumenta la confiabilidad y se reduce el estrés del convertidor, aumentando su tiempo de vida. Esta arquitectura presenta ventajas en términos económicos ya que la utilización de un transformador de múltiples devanados resulta más barata que la compra de múltiples transformadores.

Esta arquitectura sin embargo no resulta totalmente modular y requiere complejos diseños en el transformador de alta frecuencia en el que debe ser definida de forma precisa la inductancia de dispersión para cada devanado.

En la Figura 2.2 [6] se muestran las familias de arquitecturas explicadas anteriormente.

Figura 2.2: Tipos de arquitecturas SST  $\,$

El convertidor modular presenta grandes desafíos debido a la característica de su control distribuido, lo cual aumenta la complejidad y recae en que el sistema sea sincronizado a través de la comunicación. Cada etapa del convertidor es compuesta por módulos conectados en serie o paralelo como se mencionó anteriormente, donde cada uno posee una unidad de control local.

Es por esto que es necesario organizar la comunicación de forma jerárquica, orientada a maximizar la eficiencia, facilidad en el control, desempeño y minimizar los costos del convertidor. El control jerárquico es organizado en niveles, a los cuales se les brinda un objetivo específico [6].

- El primer nivel es responsable del control del voltaje y corriente haciéndose cargo del DC-link y la estrategia de modulación.

- El **segundo nivel** es responsable de la supervisión del control calculando la referencia de las señales de la etapa anterior, logrando así los objetivos del control de flujo de potencia.

- El **tercer nivel** es responsable de la coordinación de todas las etapas del convertidor. Aquí se establece el modo de operación, la adquisición de datos y la estabilidad del convertidor. Además se realiza la relación e interacción con otros elementos de la red, obteniendo datos de sus necesidades.

Figura 2.3: Diagrama y estructura de control para el SST

### 2.2. Dispositivos lógicos programables

Los dispositivos lógicos programables representan el corazón en donde el sistema de control es implementado, hoy día existen numerosas alternativas de solución lo cual puede involucrar combinaciones de estos para llegar a una solución óptima. El objetivo de este apartado es hacer una revisión de la evolución que han tenido las principales familias en la construcción de sistemas lógicos para el control y automatización con aplicaciones industriales.

Figura 2.4: Diagrama de los dispositivos lógicos programables

#### 2.2.1. Microcontroladores

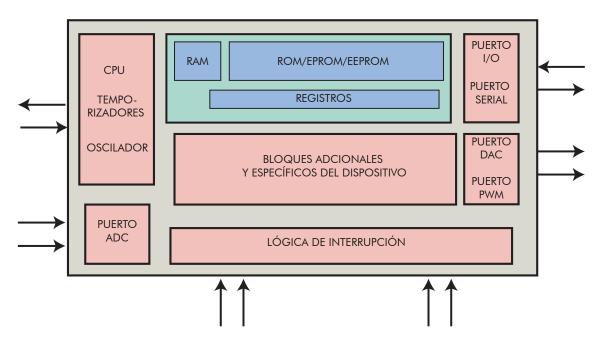

Los microcontroladores son sistemas embebidos orientados para el control y automatización de máquinas y procesos. Estos tienen una unidad de procesamiento central (CPU), memoria, puertos de entrada salida (I/O), temporizadores, contadores, conversores análogo-digital (ADC), conversores digital-análogo (DAC), puertos de comunicación, lógicas de interrupción entre otros bloques funcionales. Todos estos bloques se encuentran integrados en un solo chip de bajo consumo y de fácil integración a diseños con propósitos generales y específicos tal como se muestra en la Figura 2.5.

Durante 1970 y 1971 Intel trabajó en el desarrollo de los primeros microprocesadores. Intel 4004 fue el primer procesador de 4-bits, en el cual las instrucciones eran de 8 bits pero estas eran divididas para poder ser procesadas. En 1972 el modelo Intel 4040 aumentaba la capacidad de procesamiento añadiendo 14 nuevas instrucciones con una memoria de 8 kbits y la capacidad de tener interrupciones [13].

En 1974 Texas Instruments introdujo el primer microcontrolador TMS1000. Este modelo incluía una memoria RAM, ROM y puertos I/O en el mismo chip. Durante esos años Intel desarrollo el modelo 8085 el cual podía operar con una fuente de  $+5\mathrm{V}$  y a una frecuencia de  $3\mathrm{MHz}$ .

En paralelo Zilog con su modelo Z-80 mejoró el modelo de Intel utilizando tecnología CMOS. En 1975 Motorola introdujo al mercado su modelo 6800 seguido del 6502 y 6809.

Intel siguió el desarrollo de microcontroladores con la familia MCS-48 la cual fue rápidamente reemplazada por la MCS-51 en 1980, el cual tenía integrada una memoria de 128 bytes. Los controladores con interfaz periférica (PIC) se desarrollaron en la Universidad de Harvard durante 1975 pero no fue hasta 1985 que Microchip los lanzara al mercado, estos utilizaban la arquitectura Harvard y un set de instrucciones reducidas. Ya a fines de la década de 1970' Intel y Zilog introdujeron al mercado microprocesadores de 16 bits. En 1997 ATMEL desarrolló microcontroladores de 8-bits con arquitectura AVR caracterizados por su facilidad y simpleza de programación [13, 14].

CISC y RISC son terminologías típicas cuando se habla de microcontroladores o microprocesadores. El primer término es la abreviación de 'Computadores con Set de Instrucciones Complejas' estos microcontroladores están diseñados para reconocer una gran lista de instrucciones facilitando la flexibilidad y la reducción de líneas de escritura de los programas en lenguaje de ensamblador. El segundo término es la abreviación de 'Computadores con Set de Instrucciones Reducida', en este caso el microcontrolador sólo reconoce y ejecuta operaciones básicas como sumar o el movimiento de información entre registros. Las operaciones más complicadas se realizan al hacer una combinación de éstas (por ejemplo, la multiplicación se lleva a cabo al realizar adición sucesiva.). La ventaja de esto es que el diseño del microcontrolador necesita menos hardware, reduciendo el coste de producción y la escritura en compiladores optimizados, aumentando la velocidad de ejecución de las instrucciones. Este tipo de microcontroladores son populares dentro de las familias de PIC's de Microchip [14].

El mercado de los microcontroladores se sigue desarrollando mejorando la velocidad y capacidad de sus procesadores y presentando opciones tan diversas como las necesidades de la aplicación. A continuación se listan una serie de compañías las cuales son los principales fabricantes de microcontroladores:

- Microchip

- Texas Instruments

- ST

- NXP

- Renesas

- Maxim Integrated

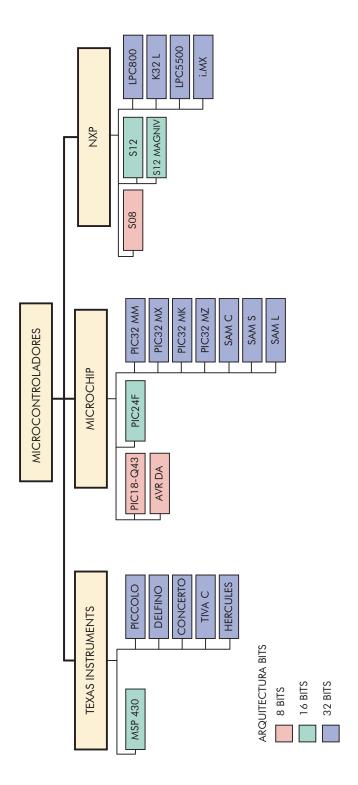

En las Tablas 2.1, 2.2 y 2.3 son expuestas las principales familias de las marcas Texas Instruments, Microchip y NXP correspondientemente con una breve descripción de sus características principales [15, 16, 17]. En la Figura 2.6 se agrupan las familias de las diferentes marcas y son clasificadas según sus bits de arquitectura.

Figura 2.5: Diagrama de los bloques funcionales de un microcontrolador

Figura 2.6: Esquema de familias de microcontroladores

Tabla 2.1: Familias de microcontroladores Texas Instruments

| FAMILIA          | n° Bits | SUBFAMILIA                         | Características                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|---------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Piccolo          | 32      | F2802x/F2803x/<br>F2805x/F2806x    | Familia de bajo consumo enfocada a aplicaciones de control en tiempo real desde electrodomésticos a accionamientos industriales. Los dispositivos tienen un procesador de hasta 90 MHz que puede operar aritmética de punto flotante. Incluye un módulo ADC de 12 bits que tiene una capacidad de muestreo de hasta 4.6 MSPS. Además de una gran conectividad mediante puertos UART, SPI, I2C, USB y CAN.                                                    |

| Delfino          | 32      | F2833x/C2834x                      | Familia de alto desempeño para aplicaciones de electrónica de potencia como inversores, fuentes de poder, radar y sensado inteligente. Los dispositivos tienen un procesador de hasta 300 MHz que opera aritmética de punto flotante. Incluye un módulo ADC de 12 bits con una capacidad de muestreo de 12.5 MSPS. Incluye puertos de comunicación UART, SPI, I2C, USB y CAN.                                                                                |

| Concerto         | 32      | F28M35Ex/<br>F28M35Mx/<br>F28M35Hx | Familia de microcontroladores de doble núcleo. Contiene un procesador C28x de hasta 150 MHz para un sub módulo de control que comparte las cualidades de las familias Piccolo. Contiene un procesador Cortex M3 de hasta 100MHz, encargado del sub módulo de comunicaciones. Ambos módulos comparten la alimentación, oscilador y memoria.                                                                                                                   |

| TIVA C<br>Series | 32      | LM4xx5Mx/<br>F28M35Hx              | Familia enfocada a aplicaciones de seguridad, domótica, HMI y control industrial. Poseen un procesador CortexM4F de hasta 80 MHz con posibilidad de modo de bajo consumo. Integra una gran cantidad de módulos para la simplificación y reducción del tamaño de la solución, en los que incluye puertos de comunicación, LDO, PWM y memorias ROM y, RAM y Flash. Soportado por su propio software TivaWare para facilitar la escritura de su código.         |

| Hercules         | 32      | RM4x/<br>TMS570LS/<br>TMS470M      | Familia de alto rendimiento dedicada a aplicaciones de seguridad industrial y médicas. Con un procesador Cortex R4F de hasta 220 MHz que soporta operaciones de punto flotante. Integra con sus periféricos opciones avanzadas de conectividad, control en tiempo real. La sub familia TMS570LS posee nucleo doble para cumplir las necesidades de seguridad en aplicaciones de trenes, automóviles y aereoespacial.                                         |

| MSP430           | 16      | MSP430FRxx                         | Familia de bajo consumo y propósito general orientada a la adquisición de datos y mediciones con módulos ADC y DAC integrados. Modulos de comunicacion SPI, UART, I2C para integración con otros dipositivos. La sub familia CapTIve añade un módulo especializado para botones o sliders capacitivos enfocados a HMI industriales. La sub familia Sistem-on-chip presenta un módulo DSP para el procesamiento de mediciones de flujómetros de ultra sonido. |

Tabla 2.2: Familias de microcontroladores Microchip

| FAMILIA       | N° BITS | Subfamilia                           | Características                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC32MM       | 32      | PIC32MMxx                            | Familia de bajo costo y consumo. Estos dispositivos presentan el puente entre los PIC24 XLP y los PIC32MX. Cuentan con un procesador de 25 MHz el cual puede combinar instrucciones de 16 y 32 bits reduciendo el espacio de la memoria.                                                                                                                                                                                                                      |

| PIC32MX       | 32      | PIC32MXxx                            | Familia de propósito general y bajo costo integra módulos para aplicaciones de audio, gráficas y de conectividad. Incluye una sub familia de bajo consumo con un procesador más potente que la familia MM. Cuentan con procesador MIPS32 MK de hasta 120 MHz y un ADC de 10 bits con una capacidad de muestreo de 1 Msps para aplicaciones industriales. Y hasta cuatro interfaces SPI e I2S para procesamiento de audio.                                     |

| PIC32MK       | 32      | PIC32MKxx                            | Familia orientada al control de motores con un gran rango de periféricos de comunicaciones. Esta familia cuenta con un procesador microAptiv de hasta 120 MHz, 7 ADC independientes de 12 bit con capacidad de 3.75 MSPS y 3 DAC de 12 bits. Además contiene un módulo DSP que permite llevar a cabo operaciones de punto flotante.                                                                                                                           |

| PIC32MZ       | 32      | PIC32MZxx                            | Familia de alto rendimiento. Posee un procesador de hasta 252MHz y una memoria flash de hasta 2Mb. Contiene una gran cantidad de periféricos para las comunicaciones USB,CAN,SPI,I2C. Un bloque DSP de doble precisión para operaciones de punto flotante y un hardware de aceleración para aplicaciones de criptografía.                                                                                                                                     |

| SAMC          | 32      | SAMC20/<br>SAMC21                    | Familia que cuenta con un procesador Cortex M0+ de hasta 48 MHz y que puede operar con un voltaje de 2.7-5 V. Poseen una gran cantidad de periféricos de comunicación cubriendo todas las aplicaciones industriales. Además de múltiples modos de operación para el reloj y de bajo consumo.                                                                                                                                                                  |

| SAML          | 32      | SAML10/<br>SAML11/<br>SAML21/ SAML22 | Familia de bajo consumo y propósito general orientada a la adquisición de datos y mediciones con módulos ADC y DAC integrados. Módulos de comunicación SPI, UART, I2C para integración con otros dispositivos. La sub familia CapTIve añade un módulo especializado para botones o sliders capacitivos enfocados a HMI industriales. La sub familia Sistem-on-chip presenta un módulo DSP para el procesamiento de mediciones de flujómetros de ultra sonido. |

| SAMS          | 32      | SAM70                                | Familia de propósito general con un procesador Cortex M7 de hasta 300 MHz de alto desempeño. Soporta operaciones de punto flotante. Contiene una gran cantidad de periféricos para cumplir con las tareas de conectividad, control, seguridad e interfaces de usuarios.                                                                                                                                                                                       |

| PIC24F        | 16      | PIC24xx                              | Familia de bajo costo y consumo que cuenta con un procesador que llega a 16MIPS. Son escalables y cuentan con un gran número de empaquetados de distintos tamaños. Cuentan con la tecnología eXtreme Low power que permite diferentes modos de bajo consumo.                                                                                                                                                                                                  |

| PIC18-<br>Q43 | 8       | PICFxxQ43                            | Familia de bajo costo que cuenta con un procesador con un velocidad de 16MIPS, de empaquetado pequeño. Cuenta con módulos ADC y PWM para desarrollar tareas de control en tiempo real. Además de periféricos de comunicación para la conectividad con otros elementos.                                                                                                                                                                                        |

| AVR<br>DA     | 8       | AVRxxDA                              | Familia orientada al control en tiempo real y para interfaces táctiles capacitivas, Cuenta con periféricos independientes al núcleo que pueden funcionar en modo de bajo consumo. Con una operación de 5 V para aumentar la inmunidad al ruido.                                                                                                                                                                                                               |

Tabla 2.3: Familias de microcontroladores NXP

| FAMILIA 1     | N° BITS | SUBFAMILIA                                                                | Características                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|---------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPC800        | 32      | LPC80x/<br>LPC81x/<br>LPC82x/<br>LPC83x/ LPC84x                           | Familia de bajo costo y consumo con empaquetados pequeños desde 24 pines. Poseen un procesador Cortex M0+ de hasta 30 MHz. Abarcan gran cantidad de aplicaciones de propósito general con módulos ADC/DAC para el control y UART/SPI/I2C para la comunicación con otros dispositivos. La presencia de estos módulos dependen del modelo de la familia. Esta familia presenta la transición de los antiguos modelos de microcontroladores de 8-16 bits a los de 32.                  |

| K32 L         | 32      | K32 L3/ K32 L2                                                            | Familia de microcontroladores diseñados para aplicación de bajo consumo y seguridad enfocadas en un ambiente de IoT. Contienen un procesador Cortex-M0 o M4 de hasta 72 MHz, además cuentan con detección de manipulación en los pines que habilitan registros de interrupción y aceleradores optimizados para tareas de criptografía.                                                                                                                                              |

| LPC5500       | 32      | LPC557x/<br>S7xLPC55S6x/<br>LPC553x/<br>S3xLPC552x/<br>S2xLPC551x/<br>S1x | Familia de microcontroladores pensada en ser la línea principal de producción para el mercado. Dependiendo de la subfamilia presentan doble núcleo y aceleración para procesamiento de señales con lo que se reduce hasta 10 veces el tiempo de tarea por ciclo de reloj. La familia posee la tecnología de 40 nm NVM que permite ser escalables en memoria y tamaño los empaquetados de los dispositivos.                                                                          |

| i.MX          | 32      | i.MX RT1170/<br>i.MX RT1064/<br>i.MX RT10xx/<br>i.MX RT600/<br>i.MXRT500  | Familia de alto desempeño que contiene núcleos múltiples que combina procesadores Cortex M7 y M4, para paralelizar el control de interfaces gráficas y el sistema de control. Contiene una arquitectura que flexibiliza el uso de memoria externas y facilita la conectividad Wireless vía Wifi, Bluetooth, Zigbee y Thread.                                                                                                                                                        |

| S12           | 16      | S12X                                                                      | Familia diseñada para aplicaciones en la industria automotriz. Los dispositivos de esta familia se caracterizan por tener empaquetados pequeños, por lo que dependiendo de la subfamilia se pueden ver microcontroladores que no presentan todos los módulos de comunicaciones, ADC o capacidad de memoria.                                                                                                                                                                         |

| S12<br>Magniv | 16      | S12Zx/ S12Vx                                                              | Familia diseñada para el control de motores, actuadores y drivers para los convertidores. Tienen un núcleo S12Z de hasta 50 MHz e incluyen interfaz CAN y LIN para la comunicación. Los modelos pueden operar hasta 20 V, integrando reguladores de tensión internos de 5 y 12 V y seis unidades para el control de Gate drivers MOSFETs reduciendo así el número de componentes para el diseño, además que los dispositivos se destacan por el tamaño pequeño de sus empaquetados. |

| S08           | 8       | SO8xx                                                                     | Familia de bajo costo en donde se encuentran productos de empaquetado robusto para ambiente industrial, bajo consumo y aplicación automotriz. Dependiendo de la sub familia presentan módulos de comunicación especializados como CAN, LIN o SPI y capacidad en su memoria.                                                                                                                                                                                                         |

### 2.2.2. Procesadores digitales de señales

Estos dispositivos comúnmente conocidos por su abreviación DSP, fueron creados en los comienzos de la década de 1980', ayudando al desarrollo de áreas que necesitan un alto nivel de cálculo como lo son la militar, aeroespacial o médica. Áreas en que el que el procesamiento de señales

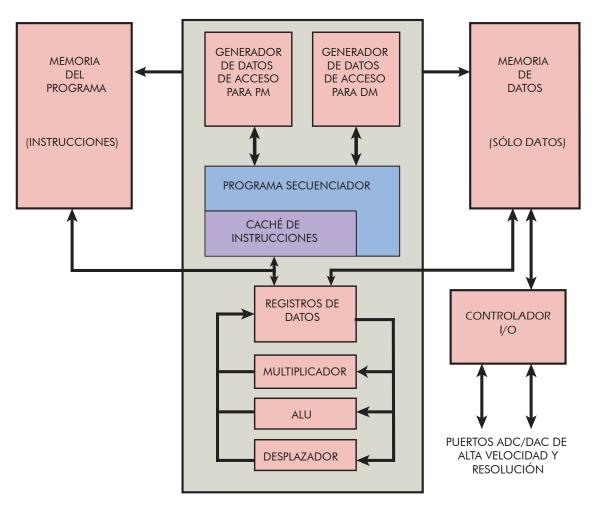

Figura 2.7: Diagrama simplificado de la arquitectura de un DSP

y la baja latencia del cálculo son parte de sus requerimientos.

Los primeros ejemplares fueron introducidos al mercado por Texas Instruments, los cuales realizaban un excelente trabajo al ejecutar operaciones de matemática de punto flotante, estos eran difíciles de programar usando sólo lenguajes de bajo nivel, dada la complejidad de las instrucciones.

El modelo i860 de Intel redujo el set de instrucciones usando una arquitectura RISC, lo que pudo llevar a los DPSs al siguiente nivel. Este modelo podía ser programado usando lenguaje C, facilitando las operaciones matemáticas de punto flotante. Como resultado el modelo i860 fue rápidamente popularizado para aplicaciones de radar e inteligencia de señales.

Aunque Intel dominó el mercado temporalmente, Freescale (actualente NXP) desarrolló una nueva tipo de arquitectura (Power Arquitecture) y el concepto de motor vectorial. Lo cual permitió que sus modelos fueran capaces de desempeñar una gran cantidad de operaciones de punto flotante por ciclo de reloj. Este conjunto de instrucciones fueron llamadas como AltiVec y fueron usadas en los procesadores de IBM, Apple y Motorola.

Luego dado factores económicos, Freescale cambió su enfoque en el comienzo de los 2000' a la telecomunicación y otros mercados siguiendo su desarrollo de AltiVec. A finales de la década Intel ganó una gran presciencia en el mercado en el área de la defensa y seguridad mientras que Freescale tuvo un nuevo auge con la introducción de los chips con multi-núcleo [18]. Hoy el futuro de los DSP's recae en los procesadores multi-núcleos, como lo son los dispositivos de la familia Xeon de Intel los cuales tienen más de 60 procesadores integrados. Esto ofrece núcleos con procesadores gráficos incluidos y una gran eficiencia en términos de operaciones por watt de potencia consumida. Otra rama de desarrollo es la combinación entre la línea más tradicional de los DSPs con otros

sistemas embebidos, como las FPGA's o microcontroladores. Usando núcleos ARM para tener procesadores gráficos incluidos en el mismo empaquetado. Haciendo estos dispositivos más autónomos, poderosos y flexibles en el diseño de sistemas digitales.

Otro avance es la inclusión de memorias internas en los chips que son usados en tarjeta, llegando a un almacenamiento del orden de los Gigabytes, disminuyendo inmensamente la latencia en sus operaciones.

Actualmente, la frontera entre microcontrolador, microprocesador y DSP es cada vez más diluida. Es fácil encontrar en el mercado microprocesadores y DSPs que incorporan memoria y periféricos internos o microcontroladores con CPUs tan potentes como las de un DSP. A veces la diferencia entre ellos es nula, y el nombre microcontrolador, microprocesador o DSP se convierte más que nada en una cuestión de marketing [19].

Los principales desarrolladores y fabricantes de DSPs son:

- Microchip

- Texas Instruments

- NXP

- Intel

- ON Semiconductor

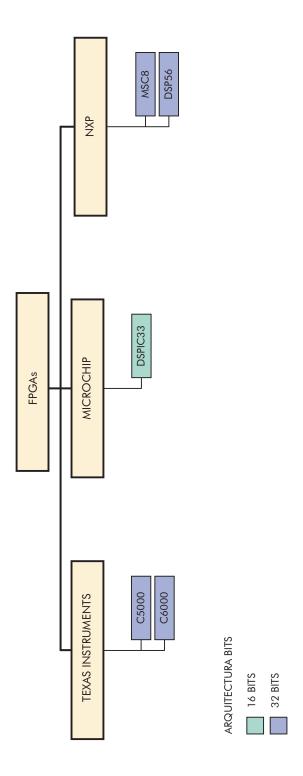

En la Tabla 2.4 se muestra una recopilación de familias de las marcas Texas Instruments, Microchip y NXP [20, 21, 22]. En la Figura 2.8 se agrupan las familias de DSPs de las marcas estudiadas.

Figura 2.8: Esquema familias DSPs

Tabla 2.4: Familias de DSPs

| MARCA             | Familia n° Bits |    | CARACTERÍSTICAS                                                                                                                                                                                                                                                                                                                 |  |

|-------------------|-----------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Texas Instruments | C5000           | 32 | Corresponde a la familia de DSP de bajo consumo con un procesador de 300 MHz que trabaja con operaciones de punto fijo. Pensada para aplicaciones gráficas, audio y voz, posee hardware de aceleración para FFT y periféricos para comunicación serial.                                                                         |  |

| Texas Instruments | C6000           | 32 | Familia multinúcleo de alto rendimiento con una velocidad de hasta 1GHz. Diseñado para aplicaciones de comunicaciones, control industrial, audio y transporte. El procesador ARM se ocupa de los periféricos de control, comunicación y captura de datos y el procesador C66 de las tareas de cálculo de punto fijo y flotante. |  |

| Microchip         | dsPIC33         | 16 | Familia de núcleo doble que opera a una velocidad máxima de 200 MHz. Diseñada para el control de motores el cual cuenta con periféricos ADC y PWM para este propósito. Familia de productos escalables con diferentes tamaños y cantidad de pines para sus empaquetados.                                                        |  |

| NXP               | MSC8            | 32 | Familia de seis núcleos, los cuales operan a 1 GHz, para tareas de alto rendimiento. Diseñado para tareas de comunicaciones inalámbricas, médicas, aeroespaciales. Contienen módulos dedicados para el procesamiento de DFT y FFT y subsistemas que soportan protocolos de redes para la transmisión correcta de datos.         |  |

| NXP               | DSP56           | 24 | Familia de DSP de doble núcleo que operan a una velocidad de 250 MHz. Diseñados para tarea de audio y video soportando los decodificadores de Dolby, THX y DTS entre otros. Esta familia cuenta con productos escalables en el número de pines permitiendo tener dispositivos de tamaño reducido.                               |  |

#### 2.2.3. FPGAs

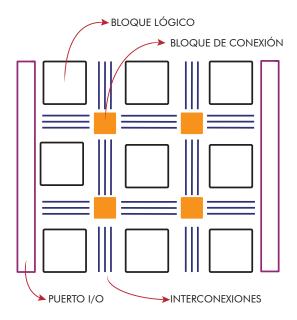

Una matriz de compuertas lógicas o FPGA es un circuito integrado que puede ser configurado después del proceso de manufactura. La FPGA se configura por medio de un lenguaje de descripción de hardware (HDL), lo cual interconecta los bloques y compuertas lógicas para la construcción de sistemas combinacionales, los cuales procesan las entradas para obtener señales de salida.

La industria de las FPGAs nació en la década de 1980' a través del desarrollo de los dispositivos lógicos programables (PLD) y las memorias programables de sólo lectura (PROM).

Estos dispositivos debían ser cableados durante el proceso de manufactura, por lo que no podían ser reprogramados.

El primer dispositivo lógico reprogramable fue el modelo EP300 de la compañía Altera en 1984. Este tenía una lámina de vidrio, que permitía que la luz ultravioleta llegase a la memoria programable (EPROM), logrando así que la configuración del dispositivo pudiera ser cambiada cuando fuera necesario.

El desarrollo de los dispositivos programables fue extendido por LuVerne R. Peterson y David W. Page quienes a mediados de la década de 1980', crearon las patentes para los bloques lógicos, compuertas y arreglos lógicos programables.

A finales de la década, la FPGA fue creada a través de los experimentos sugeridos por Steve Casselman, donde su propuesta era crear una computadora con más de 600.000 bloques reprogramables. Su trabajo fue exitoso y su creación fue patentada en 1992. A mediados de 1990', el desarrollo de la FPGA tuvo un gran impulso y revolucionó la industria en áreas como las telecomunicaciones, la automatización, la seguridad y el procesamiento de señales. En las cuales la FPGA ofrece soluciones

Figura 2.9: Arquitectura de una FPGA

de bajo costo y flexibilidad [23, 24].

La FPGA a diferencia de los microcontroladores y DSPs, procesa las señales de forma paralela siendo mucho más rápida para realizar tareas, ocupando máquinas de estados finitos. Esta no tiene un set de instrucciones preconfigurado por lo que ofrece más opciones para su programación y diseño. Es por ello que presenta una complejidad relativa para su configuración. El tiempo necesario

para la traducción del código de descripción y selección del hardware es mayor que la síntesis en microcontroladores. Por otro lado, estos dispositivos tienden a consumir más energía al no estar optimizados y sus modelos son más voluminosos y caros en comparación a los microcontroladores [25].

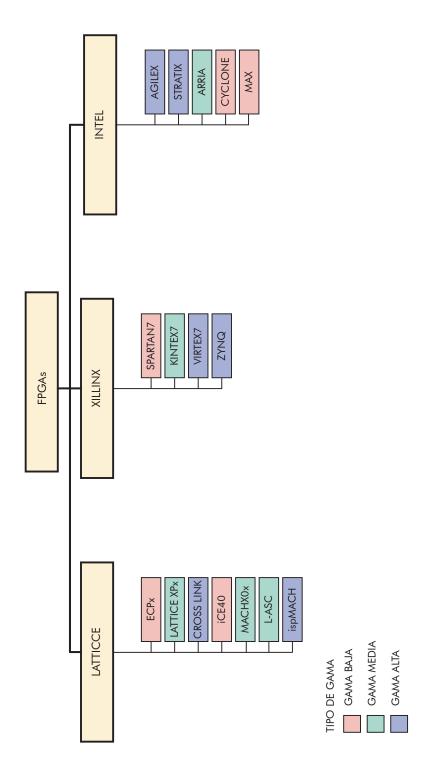

El mercado en 2020 se caracteriza por tener productores de FPGA's de propósito general y específicos dentro de los cuales se encuentran:

- Xillinx

- Intel

- Lattice

- Microchip

Las FPGAs son ocupadas en una basta cantidad de aplicaciones, una recopilación de familias existentes en el mercado se exponen en las Tablas 2.5 y 2.6.

Figura 2.10: Esquema familias FPGAs

Tabla 2.5: Familias FPGA XIllinx e Intel

| Marca   | FAMILIA  | Características                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Xillinx | SPARTAN7 | Familia dedicada a ofrecer el mejor rendimiento energético con empaquetados pequeños. Usa la tecnología de 28 nm incluyendo un procesador interno y soporte para memorias externas. Incluye ADC para aplicaciones industriales, de propósito general, conectividad y visión embebida.                                                                                                                         |

| Xillinx | KINTEX7  | Familia de gama media que usa tecnología de 28 nm. Entrega alto rendimiento usando bloques DSP en un empaquetado optimizado. Incluye periféricos para redes conectadas por fibra óptica y redes inalámbricas.                                                                                                                                                                                                 |

| Xillinx | VIRTEX 7 | Familia de alto rendimiento incluye bloques DSP, I/O de banda ancha para aplicaciones de redes $10\text{-}100\mathrm{G}$ , radar y prototipado ASIC.                                                                                                                                                                                                                                                          |

| Xillinx | ZYNQ     | Familia de alto rendimiento que posee un o dos núcleos Cortex A9 para el procesamiento junto con la lógica programable de la FPGA. Incluye memoria interna y módulos para agregar memorias externas junto con periféricos de comunicación de alta velocidad y bloques DSP. Fue diseñada para ofrecer soluciones en tareas de video vigilancia, asistencia automotriz, sistemas inalámbricos y automatización. |

| Intel   | AGILEX   | Familia dedicada a ofrecer soluciones a centro de datos, procesamiento autónomo de datos y redes. Cuenta con un procesador DSP que permite realizar operaciones de punto fijo y flotante 32 bits de alta precisión. Integra memoria y la opción de conectar una memoria externa de 16 GB soportando un ancho de banda de 512 GB/s. Posee protección contra escritura y de sus periféricos.                    |

| Intel   | STRATIX  | Familia de alto rendimiento que puede incluir un procesador Cortex A53 y bloque DSP para resolver operaciones de punto flotante. Sus aplicaciones están enfocadas en el área de la Ciber seguridad, acelerador de tareas en Data Centers, línea de comunicaciones, radar y redes.                                                                                                                             |

| Intel   | ARRIA    | Familia de rango medio que utiliza tecnología de 20 nm. Posee un núcleo doble Cortex A9 e incluye bloques DSP. Ofrece una amplia cantidad de periféricos embebidos , transceptores de alta velocidad y controladores de memoria. Sus aplicaciones se encuentran en las telecomunicaciones, centros de datos, médicas y militares.                                                                             |

| Intel   | CYCLONE  | Familia de bajo costo y consumo que usa la tecnología de 28 nm. Integra transceptores, procesador ARM y periféricos dependiendo de la subfamilia. Sus aplicaciones se ven pensadas para el control de motores, expansión de puertos I/O e interfaces.                                                                                                                                                         |

| Intel   | MAX      | Familia de bajo costo que integra gran cantidad de puertos I/O en un empaquetado reducido. Incluye ADC, bloques DSP y un procesador embebido para el proceso de tareas de control industrial y automotriz. Adaptadores de memoria externa para el almacenamiento de datos, óptimo para para video y otras aplicaciones embebidas.                                                                             |

Tabla 2.6: Familias de FPGAs Lattice

| MARCA   | FAMILIA        | Características                                                                                                                                                                                                                                               |  |

|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Lattice | ECP5 / ECP5-5G | Esta familia provee soluciones de bajo costo y consumo para implementaciones de vídeo e imagen o aplicaciones de alto volumen como sistemas de cámaras industriales, micro servidores o aplicaciones automovilísticas.                                        |  |

| Lattice | ECP3/2         | Familias de bajo costo y consumo con gran nivel de integración incluyendo bloques DSP de alto rendimiento y hasta 70000 LUTs. Soportan la mayoría de protocolos de comunicación serial de propósitos generales.                                               |  |

| Lattice | Crosslink      | Familia que soporta una gran cantidad de protocolos e interfaces para sensores y monitores. Los dispositivos están basados en la tecnología de 40nm combinando la flexibilidad y el bajo consumo. Usando módulos preconfigurados facilitando la programación. |  |

| Lattice | iCE40          | Familia de bajo consumo con empaquetados pequeños ( $< 6 \ mm^2$ ) Cuenta con transceptores internos para cámaras u otros dispositivos Pueden ser programados en una memoria no volátil a través de I2C y SPI.                                                |  |

| Lattice | MachXO(0/2/3)  | Familias orientadas al control y seguridad, cuentan con empaquetados escalables y resistentes al ambiente industrial. Los modelos cuentan con controladores SPI e I2C preimplementados junto con PPL, memorias Flash bloques RAM distribuidos.                |  |

| Lattice | ispMACH        | Familias de bajo consumo que operan a alta velocidad. Tienen un sistema de enrutamiento especializado para tener tiempos de respuestas precisos.                                                                                                              |  |

En la Tabla ?? se resume la comparación entre las familias analizadas en la sección. La información de la tabla es sólo referencial dado que existen dispositivos que pueden incluir capacidades que por lo general no es parte de su familia.

Tabla 2.7: Comparación de dispositivos lógicos programables

|                                |                                                                     | Familia Lógica Programable                                         |                           |

|--------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------|

| Característica                 | Microcontrolador                                                    | DSP                                                                | FPGA                      |

| Arquitectura en bits           | 8/16/32                                                             | 16/32                                                              | -                         |

| Consumo de Energía             | Bajo                                                                | Medio/Alto                                                         | Medio/Alto                |

| Capacidad de integración       | Alta                                                                | Baja                                                               | Alta                      |

| Programación de interrupciones | Si (Registros Dedicados)                                            | Si (Registros Dedicados                                            | Si (Lógica combinacional) |

| Paralelismo                    | No                                                                  | Si (Pseudo paralelismo a<br>través de múltiples proce-<br>sadores) | Si                        |

| Memoria interna                | Si                                                                  | Sólo algunos modelos                                               | Sólo algunos modelos      |

| Tamaño del empaquetado         | Escalables con facilidad<br>de encontrar empaqueta-<br>dos pequeños | ${\bf Medianos/Grandes}$                                           | Escalables                |

| Precio                         | Bajo                                                                | ${ m Medio/Alto}$                                                  | ${ m Medio/Alto}$         |

### 2.3. Comunicación Serie

Para comunicar a diferentes dispositivos es necesario establecer un bus de comunicación. Este regirá sobre la tasa de transmisión y la relación que tendrán para el envío y recepción de datos. A continuación se muestran los principales buses de datos que son implementados por comunicación serie.

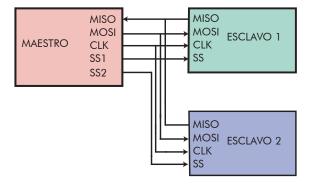

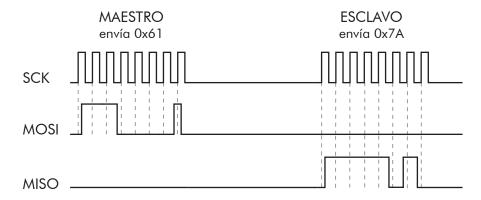

### 2.3.1. SPI (Serial Peripheral Interface)

Bus de comunicación en serie de tipo síncrono, usado ampliamente para la comunicación entre dispositivos y periféricos como sensores, ADCs, DACs y memorias. Este bus consta de dos líneas de datos, una línea de reloj y una línea de selección de esclavo.

Los términos para cada señal del protocolo son presentadas a continuación [26, 27].

- Maestro: Dispositivo que proporciona la señal de reloj para la comunicación, controla además el flujo de datos y estado de cada dispositivo.

- Esclavo: Dispositivo de comportamiento pasivo y dependiente de los comandos del maestro.

- MOSI: Master Out Slave In, es la línea por la cual el maestro envía datos a sus esclavos.

- MISO: Master In Slave Out, es la línea por la cual los esclavos envían datos al maestro.

- SCK: Línea por la cual el maestro transmite la señal de reloj.

- SS: Slave Select, línea por la cual el maestro selecciona el esclavo con quien comunicarse.

En este tipo de comunicación sólo se puede tener un maestro que controle uno o varios esclavos, por lo que todo el flujo de datos, es manejado por este. Un diagrama de la comunicación es presentado en la Figura 2.14.

Además algunas de sus características son:

- Este bus puede llegar a una velocidad de comunicación entre el rango de 10-20 Mb/s.

- Su implementación en hardware es sencilla al no necesitar resistencias pull-up.

- Permite cuatro modos de funcionamiento dependiendo de la selección de fase y polaridad del reloj para la lectura y escritura de datos.

- Debe pasar por una interfaz para poder transmitir el bus por RS-232, RS-485 o CAN.

Figura 2.11: Diagrama de comunicación SPI

Figura 2.12: Bus de transmisión SPI

### 2.3.2. I2C

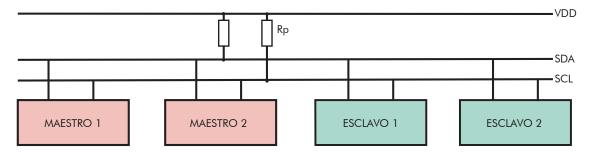

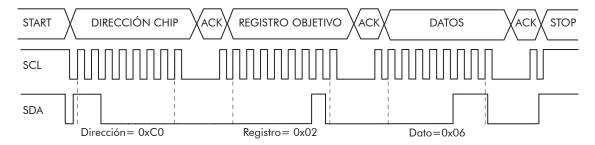

El bus I2C fue introducido en 1982 por Philips para la comunicación entre circuitos integrados. Este ha tenido varias actualizaciones durante los últimos años y es en el año 2012 con la versión V.4 fue posible llegar a velocidades de transferencia unidireccionales de hasta 5 Mb/s. I2C utiliza dos cables para todo el proceso. El protocolo I2C puede admitir más de un maestro y esclavo.

La terminología asociada al protocolo es:

- SDA: Es la línea por la que se mueven los datos entre los dispositivos.

- SCL: Es la línea de los pulsos de reloj que sincronizan el sistema.

- VDD: Línea de alimentación

- Rp: Resistencias 'Pull up' que deben ser agregadas a la línea.

El protocolo funciona de la siguiente manera. Cada dispositivo envía y recibe datos usando solo un cable que es SDA. El cable SCL mantiene la sincronización entre los dispositivos a través del reloj común que proporciona el maestro activo [28]. Cada maestro se encuentra constantemente monitoreando las señales SDA y SCL, determinando si el bus está ocupado o no, En el caso que dos o más maestros llegarán a transmitir al mismo momento, si uno de ellos detecta que SDA está en '0' y el valor a escribir es '1', asume que otro maestro está activo y termina la transferencia de bits, esto se le llama proceso de arbitraje.

Figura 2.13: Diagrama de comunicación I2C

Figura 2.14: Bus de transmisión I2C

### 2.3.3. Universal Asynchronous Receiver Transmitter (UART)

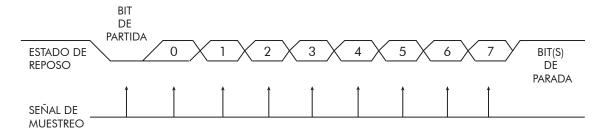

El bus UART es un estándar de comunicación serial. El registro de datos comienza con un bit de partida que es seguido con 5-9 bits de información, un bit de paridad opcional y finaliza con uno o dos bit de parada como se muestra en la Figura 2.15 [29].

Figura 2.15: Trama de bits para comunicación UART (cambiar)

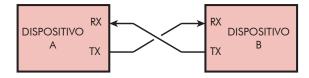

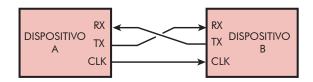

El protocolo utiliza sólo dos líneas de comunicación y puede ser configurado para ser simplex (El flujo de información sólo tiene un sentido), half duplex (Los dispositivos pueden enviar y recibir información pero se deben turnar) o full duplex (Los dispositivos pueden enviar y recibir información al mismo tiempo). Este protocolo sólo ocupa dos líneas de comunicación. Los términos que ocupa este protocolo son:

- RX: Puerto de recepción del dispositivo.

- **TX:** Puerto de transmisión del dispositivo.

Un diagrama de la comunicación es señalado en la Figura 2.16

Figura 2.16: Diagrama de comunicación UART

### 2.3.4. Universal Synchronous/Asynchronous Receiver Transmitter (USART)

Este protocolo es similar a UART, la diferencia radica en que el bus de información es acompañado por la señal de reloj que sincroniza el mensaje. En UART es el dispositvo quien

internamente genera un reloj para sincronizar el mensaje para separar y empaquetar los bits, por lo que se debe conocer el baudrate de antemano.

La transmisión de la señal de reloj permite incrementar la tasa de transmisión llegando a velocidades de 4 Mb/s. USART tiene la capacidad de generar buses más complejos adaptándose a protocolos como IrDA, LIN, RS-485 y MODBUS entre otros. Además USART puede ocuparse de forma asíncrona generando las mismas tramas de comunicación que UART. La terminología de este protocolo es [30]:

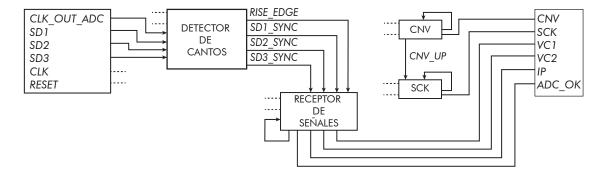

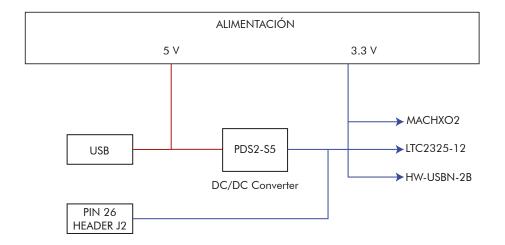

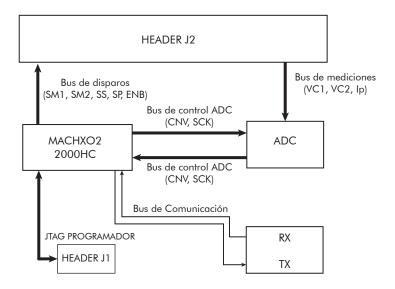

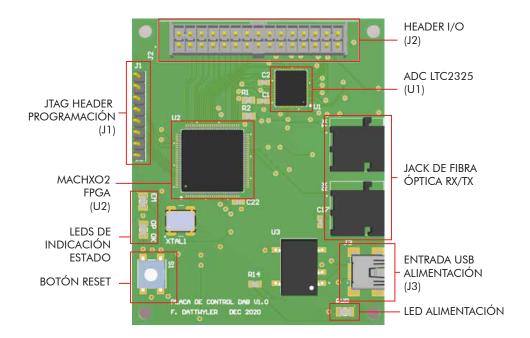

- **RX:** Puerto de recepción del dispositivo.